# **Lectures of Electrical Engineering Department**

Subject Title: Digital Electronics

Class:3rd

| Lecture sequences:  | First lecture         | <b>Instructor Name:</b> |  |  |  |  |  |

|---------------------|-----------------------|-------------------------|--|--|--|--|--|

| The major contents  | •                     |                         |  |  |  |  |  |

| 1-DRAM: definition  | n and charactaristics |                         |  |  |  |  |  |

| 2- DRAM operation   | 2- DRAM operation     |                         |  |  |  |  |  |

| 3- Design of DRAM   |                       |                         |  |  |  |  |  |

|                     |                       |                         |  |  |  |  |  |

| The detailed conten | ts:                   |                         |  |  |  |  |  |

### 1- <u>DRAM</u>

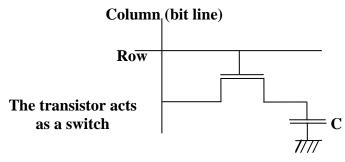

- The memory cell is capacitor and MOSFET.

- The main advantage is its higher density or more bits per <u>package</u> compared with SRAM because the memory cell is very simple compared with half of SRAM. Also the cost per bit is less in the case of DRAM.

#### **MOS DRAM Cell**

- The process (Memory refresh) is done every 5-10 ms.

- Data can be read much faster from SRAM than from DRAM.

- SRAM stored data indefinitely as long as power is applied but DRAM cannot retain very long without the capacitors being recharged by a process called refreshing.

#### 2-DRAM Operation

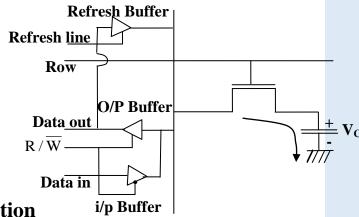

### 1) Write Operation

$$R\,/\,\overline{W}\,$$

= Low, Row = High, Refresh line = Low i/p buffer enable  $\,D_{in}=0,\,V_c=0\,$

$$D_{in}=1,\,V_c=5\,\,Volt$$

o/p buffer = disenable

#### 2) Read Operation

$$R/\overline{W}=$$

High, Row = High, Refresh line = Low o/p buffer enable  $V_c=0 \Rightarrow D_{out}="0"$   $V_c=5 \Rightarrow D_{out}="1"$

i/p buffer disenable

# 3) Refresh Operation

$R / \overline{W} = High$ , Refresh line = High, Row = High o/p buffer and refresh buffer enabled

#### **Address Multiplexing**

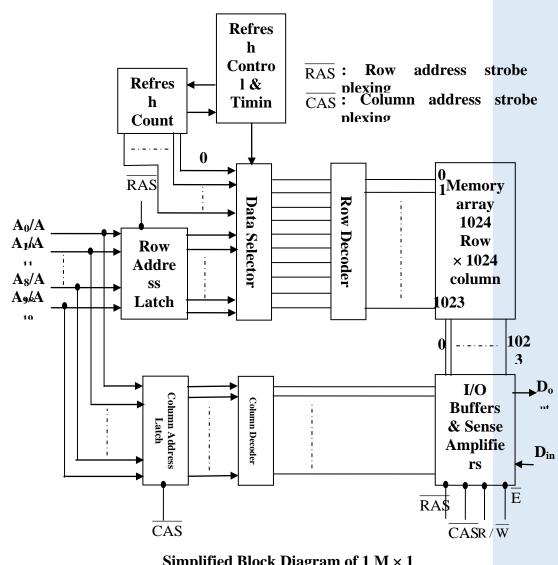

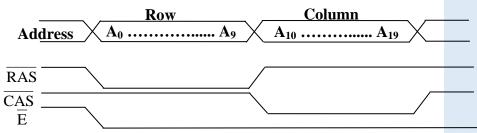

• DRAM use a technique called address multiplexing to reduce the no. of address lines and thus the number of I/O pins of the package (Chip).

#### 3- Example

For 1 M \* 1 bit DRAM. Draw the block diagram for the memory, Draw the timing for address multiplexing.

Simplified Block Diagram of  $1 \text{ M} \times 1$  DRAM

Timing diagram for address multiplexing

# **Lectures of Electrical Engineering Department**

Subject Title: Digital Electronics

Class: 3<sup>rd</sup> Electronics

| Lecture sequences: | second lecture | <b>Instructor Name:</b> |

|--------------------|----------------|-------------------------|

|--------------------|----------------|-------------------------|

The major contents:

1-A/D Converter: Characteristics

2-Flash A/D converter

3-Successive-Approximation ADC

4-Feedback Type ADC

#### The detailed contents:

#### 1- A/D Converter

**Lecture Contents**

The important ADC parameters are <u>resolution</u> and <u>throughput Resolution</u>: is the quantum of the i/p analogue voltage change required to increment its digital O/P from one <u>Code to</u> the Next <u>higher code</u>. An n-bit ADC can resolve one part in (2<sup>n</sup>-1). It may be expressed as a percentage of full scale or in bits. The resolution of 8-bit ADC can be expressed as one part in 256 or as 0.39% of full scale or simply as 8-bit resolution.

$$R = \frac{V_{ref}}{2^n}$$

#### **Throughput**

Is the sampling rate an ADC can handle in unity of samples per second (SPC).

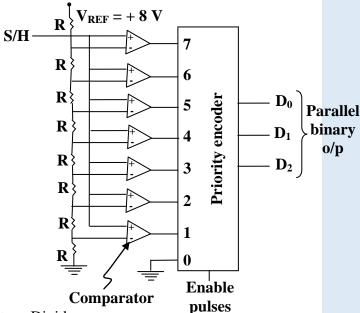

#### 2- Flash A/D Converter

(Parallel Simultaneous Converter)

- R: Resistive Voltage Divider.

3-bit Flash ADC

- No. of  $R = 2^n$ .

- No. of comparator =  $2^n$ -1.

- It is chief advantage is that it provides a fast conversion time because of a high throughput measured in sample (Per) second (SPS).

- The large no. of comparators necessary for a reasonable size binary number is one of the disadvantage of this type.

#### **Priority Encoder**

An encoder in which only the highest value input digital is encoded and any other active input is ignored.

#### **Example**

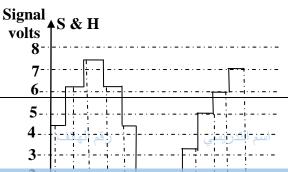

Determine the binary code output of 3-bit flash **ADC** for the i/p signal in figure and the encoder enable pulses shown consider  $V_{ref} = + 8 \text{ Volt.}$

- The frequency of enable pulses and the number of bits in the binary code, determine the accuracy with which the sequence of binary codes represents the input of the ADC.

- There should be one enable pulse for each sampled level of the input signal.

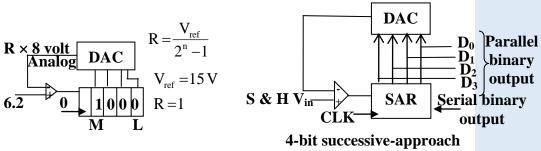

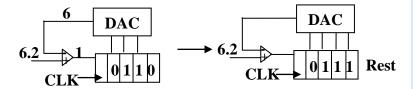

#### 3-2) Successive-Approximation ADC

**SAR:** Successive Approximation Register.

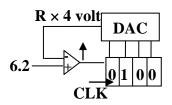

1) MSB trial:

**ADC**

2)  $2^2$  trial:

3)  $2^1$  trial:

- The final binary is equal to (0110) that reciprocal to the analogue voltage (6.2 Volt).

If  $V_{ref} = 12 \text{ Volt.}$

$R = \frac{12}{16} = 0.75 \implies \text{Code (1000)}$  binary O/P that reciprocal analog voltage  $V_A = 6.2$

Volt.

- It has much faster conversion time than the <u>Dual Slope ADC</u> but it slower than the flash ADC.

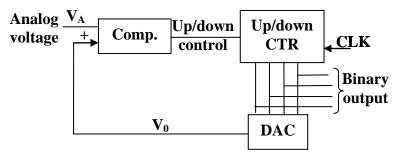

# 4-4) Feedback Type ADC

- Because of the ADC employs a ADC in its feed-back loop it is usually called a feed-back type ADC.

- The CTR counts either up or down depending on the binary level applied at its up-down control.

- The process continuous until the ADC O/P reaches the value of V<sub>A</sub> at which point the comparator switches and stops the CTR.

# **Lectures of Electrical Engineering Department**

Subject Title: Digital Electronics

Class: 3<sup>rd</sup> Electronics

| <b>Lecture sequences:</b> | Third lecture  | <b>Instructor Name:</b> |

|---------------------------|----------------|-------------------------|

| Lecture sequences:        | Tilira lecture | instructor Name         |

The major contents:

1-Performance Characteristic of DAC

2-DAC with binary-weighted resistors

3-R-2R ladder DAC

**4-DAC Errors**

#### The detailed contents:

### 1- Performance Characteristic of DAC

#### 1) Resolution:

# **Lecture Contents**

The resolution of DAC is the reciprocal of the no. of discrete steps in the output. This is of course is dependent on the no. of i/p bits.

$$R = \frac{1}{2^n - 1} * 100\%$$

For example: a 4-bit DAC has a resolution of one part in  $2^4$ -1 (One part of fifteen) expressed as a percentage  $\left(\frac{1}{15}*100\%=6.67\%\right)$ . The total no. of discrete steps equal to  $2^n$ -1 where "n" is the number of bit resolution can be expressed also by the number of bits that are converted.

#### 2) Accuracy

It is derived from a comparison of the actual output of DAC with the expected output. It is expressed as a percentage of a full scale of maximum O/P voltage. For

example of converter has a full scale O/P of 10 Volt and the accuracy is ( $\pm$  0.1%) then the maximum error for any O/P voltage is ( $10 * 0.001 = \pm 10$  mvolt).

Accuracy =

$$\pm \frac{1}{2} * \frac{1}{2^{n} - 1} * 100\% = \pm \frac{1}{2^{n+1} - 2} * 100\%$$

**For 6-bit DAC** Accuracy

$$=\pm \frac{1}{2^7-2}*100\% = \pm 0.79\%$$

**For 8-bit DAC** Accuracy

$$=\pm \frac{1}{2^9-2}*100\% = \pm 0.196\%$$

#### 3) Linearity

A linear error is a deviation from the ideal straight line output of a DAC.

A special case is an offset error which is the amount of O/P voltage when the i/p bits are all zeros.

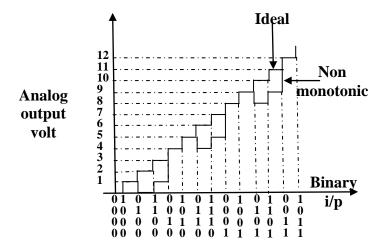

#### 4) Monotonicity

A DAC is monotonic if does not take any <u>reverse</u> steps when it is <u>sequenced</u> over its entire range of i/p bits.

### 5) **Settling Time**

It is the time between the switching of the digital inputs of the converter and the time when the O/P reaches its final value and remains within <u>specific</u> error band. It is the time required for the O/P to stabilize or change from its <u>previous</u> value to the new value corresponding to fresh digital inputs word. For a given converter the O/P does not change <u>instantaneously</u> when a change in the i/p occurs.

General purpose DAC have a settling time of several "µS" while some of the high-speed DAC have a settling time of a few "nS".

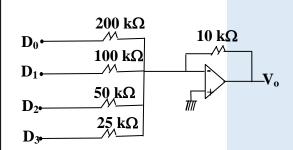

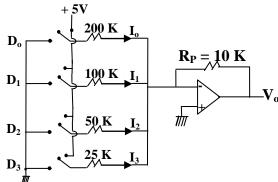

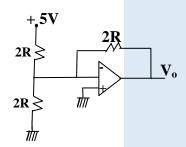

#### 1) DAC with binary-weighed resistors

N; Number of bits  $b_1$ ,  $b_2$ ,  $b_3$ , ...  $b_N$  = bits coefficient in the figure.

$b_1$  control  $S_1$ ,  $b_2$  control  $S_2$  and so on.

$$i_{_{o}}\!=\!\!\frac{V_{_{ref}}}{R}\;b_{_{1}}\!+\!\frac{V_{_{ref}}}{2R}b_{_{2}}\!+\!......\frac{V_{_{ref}}}{2^{^{N-1}}R}b_{_{n}}$$

The current through each resister is constant.

$$= \frac{2V_{ref}}{R} \left[ \frac{b_1}{2} + \frac{b_2}{4} + \frac{b_3}{8} + \frac{b_N}{2^N} \right] \text{ for 4-bit}$$

$$=\frac{2V_{ref}}{R}[D]$$

$D_{max.} = \frac{1}{2} + \frac{1}{4} + \frac{1}{8} + \frac{1}{16} = 0.9$

$$V_o = -i_o \times Rf = \frac{-2V_{ref}}{R} \frac{R}{2} \times D$$

let  $Rf = \frac{R}{2}$

$$V_o = -V_{ref} \times D$$

Let  $R = 10 \text{ K}\Omega$

MSB

$$R_1 = 10 \text{ K}\Omega$$

$N = 4\text{-bit}$

$$R_2 = 20 \text{ K}$$

$$R_3 = 40 \text{ K}$$

LSB

$$R_4 = 80 \text{ K}$$

$R_{LSB} = 2^{N-1} R_{MSB}$

- One of the disadvantage of this type of the DAC is the number of difference resistor values. For a-8-bit DAC requires 8 resistors ranging from R to 128 R.

This range of resistors requires tolerance making this type of DAC very difficult to mass-product.

- It should be noted that the accuracy of DAC depends on:-

- 1) The accuracy of  $V_{ref}$ .

- 2) The precision of the binary weighted resistor.

- 3) The perfection of switches.

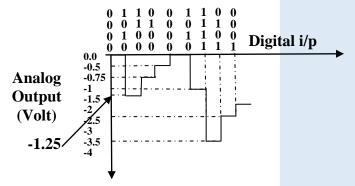

#### **Example**

Determine the output of the DAC in figure. If the sequence of 4-bit numbers shown below is applied to the inputs. The data inputs have a low value of zero volt and a high value of + 5v.

#### **Solution**

| $\mathbf{D}_3$ | $\mathbf{D}_2$ | $\mathbf{D_1}$ | $\mathbf{D_0}$ | D      | V <sub>0</sub> (Volt) |

|----------------|----------------|----------------|----------------|--------|-----------------------|

|                |                |                |                |        | = -4                  |

| 0              | 0              | 0              | 0              | 0      | 0                     |

| 0              | 1              | 0              | 1              | 0.3125 | -1.25                 |

| 0              | 0              | 1              | 1              | 0.1875 | -0.75                 |

| 0              | 0              | 1              | 0              | 0.125  | -0.5                  |

| 0              | 0              | 0              | 0              | 0      | 0                     |

| 0              | 1              | 0              | 1              | 0.3125 | -1.25                 |

| 1              | 1              | 1              | 1              | 0.9375 | -3.75                 |

| 1              | 0              | 1              | 0              | 0.625  | 25                    |

$$V_{o} = -2 \frac{V_{ref}}{R} \times Rf \times D$$

$$D = \frac{b_1}{2} + \frac{b_2}{4} + \frac{b_3}{8} + \frac{b_4}{16}$$

$$=\frac{0}{2}+\frac{1}{4}+\frac{0}{8}+\frac{1}{16}$$

$$=0.3125$$

$$V_{o} = \frac{-2 \times 5}{25} \times 10 \times D$$

$$I_o = \frac{5}{200} = 0.025 \,\text{mA} \implies V_o \equiv I_o \,\text{Rf} = 0.25 \,\text{volt}$$

$$I_1 = \frac{5}{100} = 0.05 \,\text{mA} \implies V_0 \equiv I_1 \,\text{Rf} = 0.5 \,\text{volt}$$

$$I_2 = \frac{5}{50} = 0 \,\text{mA} \implies V_o \equiv -1 \,\text{volt}$$

| $D_3$ | $\mathbf{D}_2$ | $\mathbf{D}_1$ | $\mathbf{D}_0$ | في حالة                |

|-------|----------------|----------------|----------------|------------------------|

| 0     | 0              | 0              | 0              | 0                      |

| 0     | 1              | 0              | 1              | -1.25                  |

| 0     | 0              | 1              | 1              | -0.25 - 0.5 = -0.75  V |

|       |                |                |                |                        |

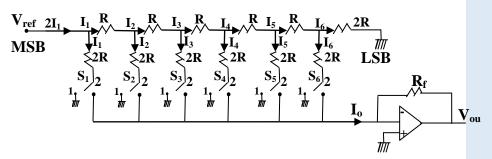

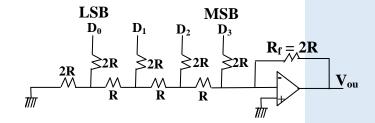

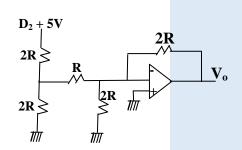

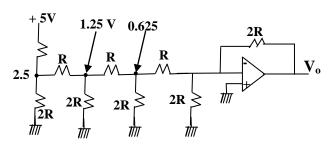

### 2) 3-R-2R Ladder DAC

$$I_0 = I_1 b_1 + I_2 b_2 + I_3 b_3 + \dots + I_N b_N$$

N: no. of bits

$$I_1 = 2I_2, I_2 = 2I_3, I_3 = 2I_4$$

$$I_1 = 4I_3 = 8I_4 = 16I_5 = 32I_6, 2^{n-1}I_N$$

$$I_o = I_1 b_1 + \frac{I_1 b_2}{2} + \frac{I_1 b_3}{4} + \frac{I_1 b_4}{8} \dots + \frac{b_N I_1}{2^{N-1}}$$

$$I_0 = 2I_1 * D$$

$$I_1 = \frac{V_{ref}}{2R} \qquad V_{out} = -I_o * Rf$$

$$=-2R\frac{V_{ref}D}{2R}=Rf$$

General

If

$$Rf = R$$

$V_{out} = -V_{ref} * D$  (only when  $Rf = R$ )

Analog O/P Digital

R-2R ladder DAC overcomes one of the problem in the binary-weighted DAC is that it requires only two resistances (R, 2R) (i.e. Small Spread in resistance values). For this reason the R-2R DAC considered the more common type.

#### **Example**

Find the output voltage when:

- 1) Only  $D_0 = 1$ .

- 2)

- 3) Only  $D_1 = 1$ .

- 4) Only  $D_2 = 1$ .

- 5) Only  $D_3 = 1$ .

# **Solution**

<u>Method (1)</u>:-

1)

$$D_3 = 1$$

$D_0 = D_1 = D_2 = 0$

$$I_o = \frac{5}{2R} \qquad \because V_o = I_o Rf$$

$$= \frac{-5}{2R} * 2R = -5 \text{ Volt}$$

2)

$$D_2 = 1$$

$D_0 = D_1 = D_3 = 0$

$$I_o = \frac{2.5}{2R}$$

$V_o = -i_o * Rf$

$$= \frac{-2.5}{2R} * 2R = 2.5 \text{ Volt}$$

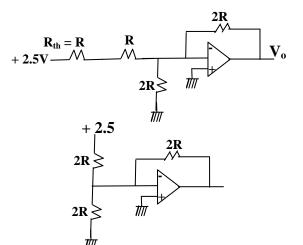

3)

$$D_1 = 1$$

$D_0 = D_2 = D_3 = 0$

$$R_{th} = R \qquad R \qquad V_0$$

$$I_o = \frac{1.25}{2R} \Rightarrow V_o = \frac{-1.25}{2R} = 2R$$

$$= -1.25 \text{ Volt}$$

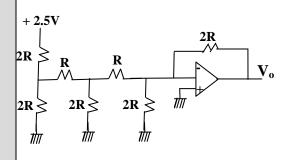

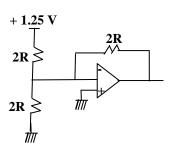

4)

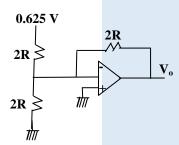

$$D_0 = 1$$

$D_1 = D_2 = D_3 = 0$

$V_0 = -0.625 \text{ Volt}$

$$\begin{split} & \text{if} \quad D_o = D_1 = D_2 = D_3 = 1 \\ & V_o = (\text{-}5) + (\text{-}2.5) + (\text{-}1.25) + (\text{-}0.625) \\ & = \\ & \text{if} \quad D_o = D_3 = D_1 = 1, \ D_2 = 0 \\ & V_o = \text{-}5 + \text{-}1.25 + \text{-}0.625 \end{split}$$

#### Method (2):

$$V_o = -2 \frac{V_{ref}}{2R} *D*Rf$$

$$If \quad D_3 = 1 \quad D_1 = D_o = D_2 = 0 \qquad D = \frac{b_1}{2} + \frac{b_2}{4} + \frac{b_3}{8} + \frac{b_4}{16}$$

جامعة الموصل/ كلية الهندسة

$$V_o = -2*\frac{5}{2R}*\frac{1}{2}*2R \qquad \qquad = \frac{1}{2}+0+0+0$$

$$= -5 \text{ Volt}$$

# 4- DAC Errors

# **NON Monotonicity**

In this particular case, the error occurs because 21 bit in binary code is "0" that is a short is causing the bit input-line to be stuck in low.

|   | i/ | 'p |   | o/p<br>(after) | o/p<br>(before) |

|---|----|----|---|----------------|-----------------|

| 0 | 0  | 0  | 0 | 0              | <del>0</del>    |

| 0 | 0  | 0  | 1 | 1 —            | <b>→</b> 1      |

| 0 | 0  | 1  | 0 | 0              | →2              |

| 0 | 0  | 1  | 1 | 1              | → 3             |

| 0 | 0  | 0  | 0 | 4              | <b>→</b> 4      |

| 0 | 1  | 0  | 1 | 5              | <b>→</b> 5      |

| 0 | 1  | 1  | 0 | 4              | <b>→</b> 6      |

| 0 | 1  | 1  | 1 | 5              | <b>→</b> 7      |

| 1 | 0  | 0  | 0 | 8              | <b>→</b> 8      |

| 1 | 0  | 0  | 1 | 9              | <b>→</b> 9      |

| 1 | 0  | 1  | 0 | 8              | <b>→ 10</b>     |

| 1 | 0  | 1  | 1 | 9              | <b>→11</b>      |

| 1 | 1  | 0  | 0 | 12             | <b>→12</b>      |

## **Example**

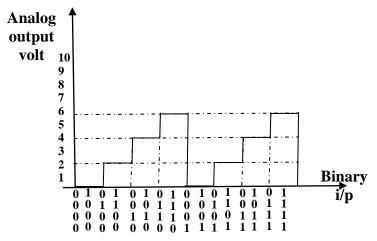

A straight binary sequence is applied to a 4-bit DAC and the O/P in figure (1) is observed. What is the problem? Identify the error?

# **Solution**

| ]     | Bina  | ry I/          |                       | Analog O/P          | Correct     |

|-------|-------|----------------|-----------------------|---------------------|-------------|

| $2^3$ | $2^2$ | 2 <sup>1</sup> | <b>2</b> <sup>0</sup> |                     |             |

| 0     | 0     | 0              | 0                     | <b>→</b> 1 <b>─</b> | <b>→</b> 0  |

| 0     | 0     | 0              | 1                     | <b>→</b> 1 <b>—</b> | <b>→</b> 1  |

| 0     | 0     | 1              | 0                     | <b>→</b> 3 <b>─</b> | <b>→</b> 2  |

| 0     | 0     | 1              | 1                     | <b>→</b> 3 <b>─</b> | <b>→</b> 3  |

| 0     | 1     | 0              | 0                     | <b>→</b> 1 <b>—</b> | <b>→</b> 4  |

| 0     | 1     | 0              | 1                     | <b>→</b> 1 <b>—</b> | <b>→</b> 5  |

| 0     | 1     | 1              | 0                     | <b>→</b> 3 <b>─</b> | <b>→</b> 6  |

| 0     | 1     | 1              | 1                     | <b>→</b> 3 <b>−</b> | <b>→</b> 7  |

| 1     | 0     | 0              | 0                     | <b>→</b> 9 <b>─</b> | → 8         |

| 1     | 0     | 1              | 0                     | <b>→11</b>          | <b>→ 10</b> |

| 1     | 0     | 1              | 1                     | <b>→ 11</b>         | <b>→</b> 11 |

| 1     | 1     | 0              | 0                     | <b>→</b> 9          | <b>→</b> 12 |

| 1     | 1     | 0              | 1                     | <b>→</b> 9          | <b>→</b> 13 |

| 1     | 1     | 1              | 0                     | <b>→11</b>          | <b>→ 14</b> |

| 1     | 1     | 1              | 1                     | <b>→</b> 11         | <b>→</b> 15 |

|       |       |                |                       |                     |             |

2° stuck in high

2° stuck in low

The error is non-monotonic

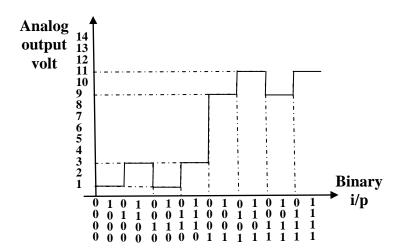

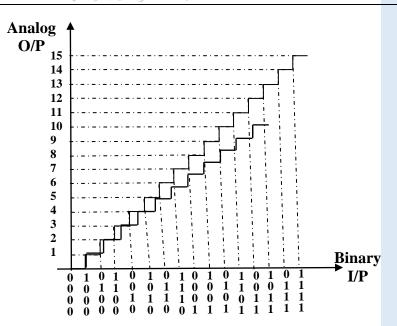

#### **Example**

If the first and the last bit are both stuck in low in a 4-bit DAC what will be the O/P? Draw it?

• Straight binary sequence that applied to.

| E | 3ina: | ry i/ | p Analog o/p          | Correct |

|---|-------|-------|-----------------------|---------|

| 0 | 0     | 0     | 0                     | 0       |

| 0 | 0     | 0     | $1 \longrightarrow 0$ | 1       |

| 0 | 0     | 1     | $0 \longrightarrow 2$ | 2       |

| 0 | 0     | 1     | 1 2                   | 3       |

| 0 | 1     | 0     | 0                     | 4       |

| 0 | 1     | 0     | 1 4                   | 5       |

| 0 | 1     | 1     | $0 \longrightarrow 6$ | 6       |

| 0 | 1     | 1     | 1 6                   | 7       |

| 1 | 0     | 0     | $0 \longrightarrow 0$ | 8       |

| 1 | 0     | 0     | 1 0                   | 9       |

| 1 | 0     | 1     | $0 \longrightarrow 2$ | 10      |

| 1 | 0     | 1     | $1 \longrightarrow 2$ | 11      |

| 1 | 1     | 0     | $0 \longrightarrow 4$ | 12      |

| 1 | 1     | 0     | 1                     | 13      |

| 1 | 1     | 1     | $0 \longrightarrow 6$ | 14      |

| 1 | 1     | 1     | 1 6                   | 15      |

|   |       |       |                       |         |

#### 2) Non Linearity

Figure shown illustrates non-linearity in which the step amplitude is <u>less than</u> it should be for certain input codes. This <u>particular</u> output could be caused by the 2<sup>2</sup> bit having an <u>insufficient weight</u>, perhaps because of a <u>faulty</u> input resistor. We could also <u>see steps</u> with amplitudes <u>greater than normal</u> if a <u>particular</u> binary weight were <u>greater than it should be</u>.

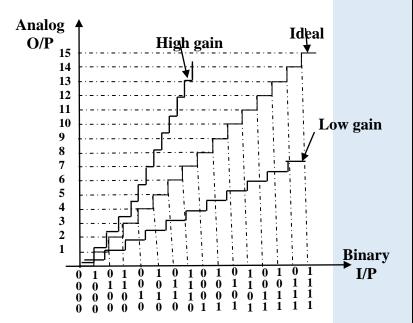

#### 3) Low and High Gain

Output error caused by low or high gain are illustrated in figure.

In this case of low gain all of the step amplitudes are less than ideal.

In this case of high gain, all of the step amplitudes are greater than ideal. This situation may be caused by a faulty feedback resistor in the OP. amp circuit.

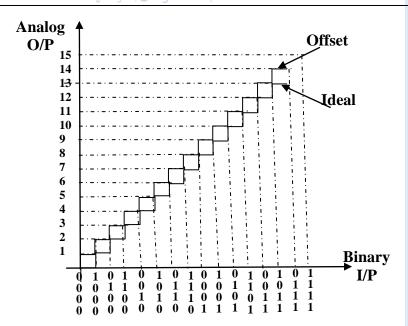

#### 4) Offset Error

An offset error is illustrated in figure. Notice that when the binary input is (0000) the output voltage is nonzero and that this amount of offset is the same for all steps in the conversion. A faulty OP-amp be the <u>culprit in</u> this situation.

عنوان البريد الاليكتروني

رقم الهاتف

اسم التدريسي

It is not possible to manufacture amplifier with perfectly matched <u>transistor</u> and <u>resistors</u>. The <u>mismatch creates</u> a dc. offset error in the O/P with no differential dc. i/p. The dc. o/p of an op-amp should ideally be <u>zero</u> volts with respect to ground. Any <u>deviation</u> from this is known as <u>dc. offset error</u>.

# **Lectures of Electrical Engineering Department**

# Subject Title: Digital Electronics

Class: 3<sup>rd</sup> Electronics

| Lecture | <b>Lecture sequences:</b> |  |   | Fourth lecture | <b>Instructor Name:</b> |

|---------|---------------------------|--|---|----------------|-------------------------|

| /TOI    | •                         |  | - |                |                         |

The major contents:

- 1-Sequential Logic Circuits: Definition and Characteristics

- 2- The types of sequential logic circuits

- **3-General Design Procedure of Sequential Circuit**

#### The detailed contents:

#### 1- Sequential Logic Circuits

# **Lecture Contents**

The logic circuits can be divided by two categories:

- 1) Combinational circuit is one where the O/P at any time depends <u>upon</u> only <u>on</u> <u>the present</u> combination of inputs at the point of time with total <u>disregard</u>. To the past state of the inputs. The logic gate is the most basic building block of combinational logic.

- 2) Sequential logic circuit: The output in it depends up on <u>not only</u> the <u>present</u> but also the <u>past state</u> of <u>inputs</u>.

- Sequential circuit Comprises both logic gate and memory elements such as Flip-Flop.

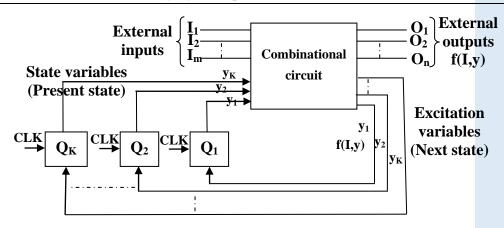

**Block diagram of a sequential circuit (Synchronous)**

- Present contents of memory elements is referred as the present state. The new

contents of the memory elements are referred as next state and depend upon the

external input and present state.

- Not all sequential circuit have i/p and O/P variables as in the general model just discussed. However, <u>all have excitation</u> variables and state variables. For example, N-bit <u>gray</u> code counter has no i/PS other than <u>clock</u> and <u>no O/PS other than it's internal state (O/PS are taken off each F.F in the counter).</u>

- 2- Sequential circuits are divided into two main types:

- 1) Synchronous sequential circuits: <u>change their state</u> and O/P values at discrete instants of time (clock signal). The memory elements <u>used in synchronous circuits</u> are usually <u>Flip-Flop</u>.

- 2) Asynchronous: The <u>transition</u> from one state to another is initiated by the change in the <u>primary i/ps</u>, there is no external <u>synchronization</u>. The memory <u>commonly</u> used in it are <u>time delayed</u> devices.

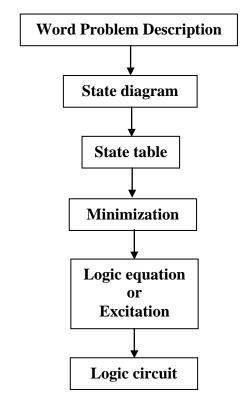

# 3-General Design Procedure of Sequential Circuit

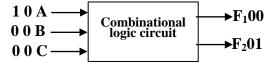

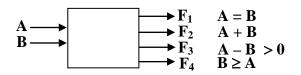

#### 1) Combinational circuit

عنوان البريد الاليكتروني

رقم الهاتف

اسم التدريسي

| A | В | $\mathbf{F_1}$   | $\mathbf{F}_2$ | $\mathbf{F}_3$ | $\mathbf{F_4}$ |

|---|---|------------------|----------------|----------------|----------------|

| 0 | 0 | 1<br>0<br>0<br>1 | 0              | 0              | 1              |

| 0 | 1 | 0                | 1              | 0              | 1              |

| 1 | 0 | 0                | 1              | 1              | 0              |

| 1 | 1 | 1                | 0              | 0              | 1              |

|   |   |                  |                |                |                |

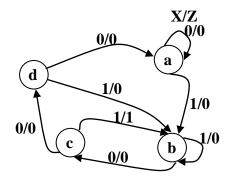

#### 2) Sequential circuit

External i/p  $(X_1, X_2, ... X_n)$

External o/p  $(Z_1, Z_2, ... X_n)$

$\left. \begin{array}{l} \text{Present State } (y_1, \, y_2, \, \, \ldots \, y_K) \\ \text{Next State } (Y_1, \, Y_2, \, \, \ldots \, Y_K) \end{array} \right\} \text{Memory}$

#### **Examples**

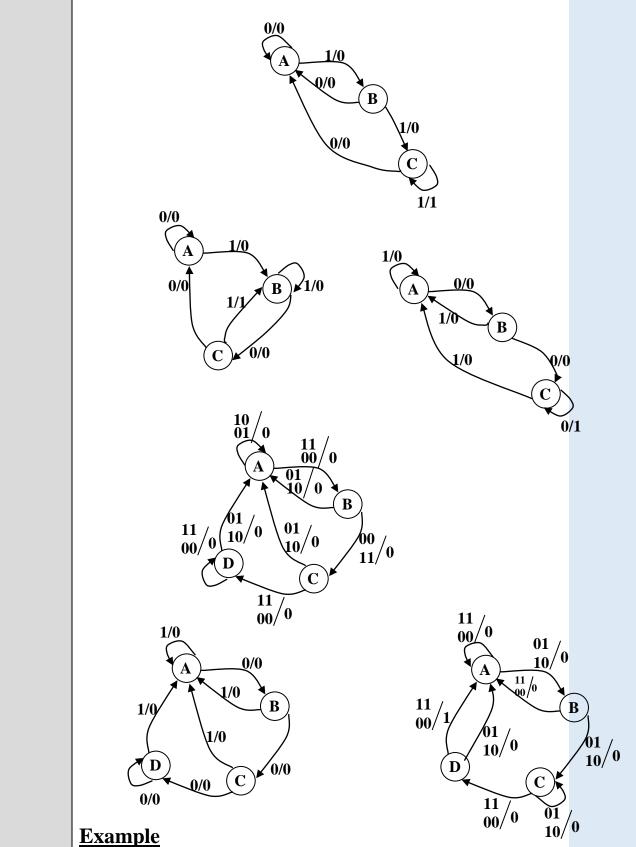

Construct the state diagram for a simplified circuit <u>a soda vending Machine</u> with a single input and single output. The input is one of two coins deposited (<u>dimes</u> or quarters). The O/P is a binary signal with "0" <u>indicating</u> no can of soda <u>is released</u> and 1 indicating a can is released. Assume the cost of a can of soda is 35 cent.

## State diagram

## تصميم الدوائر الالكترونية:

- (P.S.) الحالة اللاحقة (P.S.) الحالة التصميم على شكل مخطط يبين الانتقال من الحالة السابقة (P.S.) الحالة اللاحقة (N.S.)

- 2- تحويل مخطط انتقال الحالات المتتالية إلى جدول يبين انتقال بين الحالات ويبين اخراجات باختلاف الحالات والادخالات.

3- عمل جدول تنظيمي (Implication Chart) لتقليص الحالات المتشابهة واختزالها إلى حالة واحدة.

| P.S | NS    | S/ <b>Z</b> |

|-----|-------|-------------|

| 1.5 | X = 0 | X = 1       |

| a   | a/o   | b/o         |

| b   | c/o   | b/o         |

| c   | d/o   | <b>b/1</b>  |

| d   | a/o   | b/o         |

4- نعيد كتابة الجدول من جديد بعد حالات الاختزال.

| b | X |     |   |

|---|---|-----|---|

| c | X | X   |   |

| d | > | a≽c | X |

|   | a | b   | С |

| P.S | - 12  | S/Z        |

|-----|-------|------------|

| 1.5 | X = 0 | X = 1      |

| a   | a/o   | b/o        |

| b   | c/o   | b/o        |

| c   | a/o   | <b>b/1</b> |

5- تحديد عدد المراجيح اللازمة في التصميم وفق المعادلة التالية.

For example  $2^{n-1} < NS \le 2^n$

NS=3

2 113 32

$\therefore$  n = 2 2<3 \le 4 n: no. of flop-flops

6- بعد اختيار عدد (F/F) نقوم بترميز الجدول.

7- تحدید نوع الـ T, RS, JK, D (F/F)

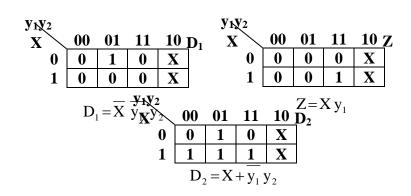

| NS    | S/Z                   |

|-------|-----------------------|

| X = 0 | X = 1                 |

| 00/0  | 01/0                  |

| 11/0  | 01/0                  |

| 00/0  | 01/1                  |

|       | X = 0<br>00/0<br>11/0 |

when: NS: no. of states.

| P.S<br>Q <sub>n</sub> (y) | $N.S \\ Q_{n+1}(y)$ | D | J- | K            | R | -S | Т |

|---------------------------|---------------------|---|----|--------------|---|----|---|

| 0                         | 0                   | 0 | 0  | $\mathbf{X}$ | X | 0  | 0 |

| 0                         | 1                   | 1 | 1  | $\mathbf{X}$ | 0 | 1  | 1 |

| 1                         | 0                   | 0 | X  | 1            | 1 | 0  | 1 |

|                           |                     |   |    |              |   | X  |   |

**Excitation table**

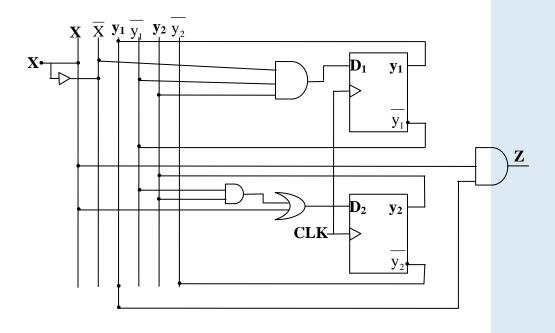

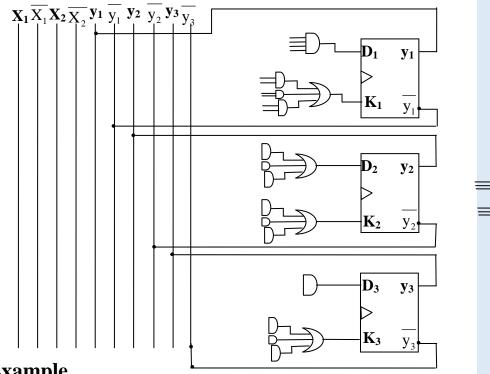

# Choose D-flip-flop in the design

(Z) و نقوم بعمل خارطة كارنو لإيجاد  $(D_1 \text{ and } D_2)$  و (Z)

| P                  | .S             | <b>X</b> :       | = 0              | -              |                | X = 1          |                  |                |                |

|--------------------|----------------|------------------|------------------|----------------|----------------|----------------|------------------|----------------|----------------|

| $\ \mathbf{y_1}\ $ | $\mathbf{y}_2$ | $\mathbf{Y}_{1}$ | $\mathbf{Y}_{2}$ | $\mathbf{D}_1$ | $\mathbf{D_2}$ | $\mathbf{Y_1}$ | $\mathbf{Y}_{2}$ | $\mathbf{D}_1$ | $\mathbf{D_2}$ |

| 0                  | 0              | 00               | /0               | 0              | 0              | 01             | /0               | 0              | 1              |

| 0                  | 1              | 11               | /0               | 1              | 1              | 01             | <b>1/0</b>       | 0              | 1              |

| 1                  | 1              | 00               | 0/0              | 0              | 0              | 01             | /1               | 0              | 1              |

#### 9- رسم الدائرة المنطقية.

# **Example**

Minimize the transition table (State table) below and complete the design of the system (Use J-K-Flip-Flop) then draw the logic circuit.

| В | X            | ]                   |          |             |     |     |   |

|---|--------------|---------------------|----------|-------------|-----|-----|---|

| C | X ·          | <b>A</b> =F         |          |             |     |     |   |

| D | A₹F          | X                   | X        |             |     |     |   |

|   | B=D          |                     |          |             | _   |     |   |

| E | X            | A≠F                 | Ď≠F      | X           |     |     |   |

|   | _            | <b>B</b> = <b>D</b> | /\       |             |     |     |   |

| F | <b>√</b> A=F | X                   | X        | ₿¥D         | X   |     |   |

| G | ₽ĘG          | X                   | X        | <b>Ą</b> ≒F | X   | Ą≠F |   |

|   | Æ¥F          |                     |          | B¥G         |     | DĞG |   |

|   |              |                     |          | Ď=Ġ         |     |     |   |

| H | X            | B≠C                 | B≂C      | X           | B≠C | X   | X |

|   |              | <b>A</b> =F         | <b>√</b> |             | Ø≥F |     |   |

|   | A            | В                   | C        | D           | E   | F   | G |

|   |              |                     |          |             |     | ·   |   |

|     | $X_1X_2$                      | $X_1X_2$                              | $X_1X_2$                        | $X_1X_2$                              |

|-----|-------------------------------|---------------------------------------|---------------------------------|---------------------------------------|

| P.S | $\frac{\mathbf{A_1 A_2}}{00}$ | $\frac{\mathbf{A}_1\mathbf{A}_2}{01}$ | $\frac{\Lambda_1\Lambda_2}{10}$ | $\frac{\mathbf{A}_1\mathbf{A}_2}{11}$ |

| A   | <b>D</b> /0                   | <b>D</b> /0                           | F/0                             | A/0                                   |

| В   | C/1                           | <b>D</b> /0                           | E/1                             | F/0                                   |

| C   | C/1                           | <b>D</b> /0                           | E/1                             | <b>A/0</b>                            |

| D   | $\mathbf{D}/0$                | B/0                                   | A/0                             | F/0                                   |

| E   | C/1                           | F/0                                   | E/1                             | <b>A/0</b>                            |

| F   | $\mathbf{D}/0$                | <b>D</b> /0                           | A/0                             | F/0                                   |

| G   | <b>G</b> /0                   | G/0                                   | <b>A/0</b>                      | <b>A/0</b>                            |

| H   | <b>B/1</b>                    | <b>D</b> /0                           | E/1                             | <b>A/0</b>                            |

$$B = C = H$$

$$A = F$$

$$B = H$$

$$H = C$$

| P.S | $X_1X_2$       | $X_1X_2$    | $X_1X_2$   | $X_1X_2$   |

|-----|----------------|-------------|------------|------------|

| 1.5 | 00             | 01          | 10         | 11         |

| A   | <b>D</b> /0    | <b>D</b> /0 | A/0        | A/0        |

| В   | <b>B</b> /1    | <b>D</b> /0 | <b>E/1</b> | <b>A/0</b> |

| D   | $\mathbf{D}/0$ | <b>B</b> /0 | <b>A/0</b> | <b>A/0</b> |

| E   | <b>B</b> /1    | <b>A/0</b>  | <b>E/1</b> | <b>A/0</b> |

| G   | <b>G/0</b>     | <b>G/0</b>  | <b>A/0</b> | <b>A/0</b> |

|                |                |                       | $\mathbf{X}_1\mathbf{X}_2=0$ | $\mathbf{X}_1\mathbf{X}_2=01$ | 10            | 11            |

|----------------|----------------|-----------------------|------------------------------|-------------------------------|---------------|---------------|

| $\mathbf{y_1}$ | $\mathbf{y}_2$ | <b>y</b> <sub>3</sub> | $Y_1Y_2Y_3/Z$                | $Y_1Y_2Y_3/Z$                 | $Y_1Y_2Y_3/Z$ | $Y_1Y_2Y_3/Z$ |

| 0              | 0              | 0                     | 011/0                        | 011/0                         | 000/0         | 000/0         |

| 0              | 0              | 1                     | 001/1                        | 011/0                         | 111/1         | 000/0         |

| 0              | 1              | 1                     | 011/0                        | 001/0                         | 000/0         | 000/0         |

| 1              | 1              | 1                     | 001/1                        | 000/0                         | 111/1         | 000/0         |

| 1              | 1              | 0                     | 110/0                        | 110/0                         | 000/0         | 000/0         |

|                |                |                       | 00               |               | 00 01            |               | 10               |               | 11               |               |

|----------------|----------------|-----------------------|------------------|---------------|------------------|---------------|------------------|---------------|------------------|---------------|

| $\mathbf{y_1}$ | $\mathbf{y}_2$ | <b>y</b> <sub>3</sub> | $\mathbf{Y}_{1}$ | $J_1K_1$      | $\mathbf{Y}_{1}$ | $J_1K_1$      | $\mathbf{Y}_{1}$ | $J_1K_1$      | $\mathbf{Y}_{1}$ | $J_1K_1$      |

| 0              | 0              | 0                     | 1                | 1X            | 1                | 1X            | 0                | <b>0X</b>     | 0                | 0X            |

| 0              | 0              | 1                     | 0                | $\mathbf{0X}$ | 1                | 1X            | 1                | 1X            | 0                | $\mathbf{0X}$ |

| 0              | 1              | 1                     | 1                | $\mathbf{X0}$ | 0                | <b>X1</b>     | 0                | <b>X1</b>     | 0                | <b>X1</b>     |

| 1              | 1              | 1                     | 0                | <b>X1</b>     | 0                | <b>X1</b>     | 1                | $\mathbf{X0}$ | 0                | <b>X1</b>     |

| 1              | 1              | 0                     | 1                | $\mathbf{X0}$ | 1                | $\mathbf{X0}$ | 0                | <b>X1</b>     | 0                | <b>X1</b>     |

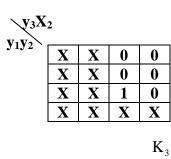

| <b>у</b> <sub>3</sub> Х | ζ <sub>2</sub> |    |    | $\overline{X_1} =$ | 0  |

|-------------------------|----------------|----|----|--------------------|----|

| $y_1y_2$                |                | 00 | 01 | 11                 | 10 |

| (                       | 00             | 0  | 0  | 0                  | 0  |

| (                       | 01             | X  | X  | 0                  | 0  |

| -                       | 11             | X  | X  | X                  | X  |

|                         | 10             | X  | X  | X                  | X  |

| $y_3X_2$ $y_1y_2$ |   |   | $\Lambda_1 =$ | -1 |

|-------------------|---|---|---------------|----|

| `                 | 0 | 0 | 0             | 1  |

|                   | X | X | 0             | 0  |

|                   | X | X | X             | X  |

|                   | Y | Y | Y             | Y  |

| $y_3X$ $y_1y_2$ | 2 | $X_1$ | =1 |   |

|-----------------|---|-------|----|---|

| J1J2            | X | X     | X  | X |

|                 | X | X     | X  | X |

|                 | 1 | 1     | 1  | 0 |

|                 | X | X     | X  | X |

$$K_1 = \overline{X_1} y_3 + X_1 \overline{y_3} + X_1 X_2$$

|                |       |                       | 00               |               | 01               |               | 10               |               | 11             |               |

|----------------|-------|-----------------------|------------------|---------------|------------------|---------------|------------------|---------------|----------------|---------------|

| $\mathbf{y_1}$ | $y_2$ | <b>y</b> <sub>3</sub> | $\mathbf{Y}_{1}$ | $J_1K_1$      | $\mathbf{Y}_{1}$ | $J_1K_1$      | $\mathbf{Y}_{1}$ | $J_1K_1$      | $\mathbf{Y_1}$ | $J_1K_1$      |

| 0              | 0     | 0                     | 1                | 1X            | 1                | 1X            | 0                | <b>0X</b>     | 0              | <b>0X</b>     |

| 0              | 0     | 1                     | 0                | $\mathbf{0X}$ | 1                | 1X            | 1                | 1X            | 0              | $\mathbf{0X}$ |

| 0              | 1     | 1                     | 1                | $\mathbf{X0}$ | 0                | <b>X1</b>     | 0                | <b>X1</b>     | 0              | <b>X1</b>     |

| 1              | 1     | 1                     | 0                | <b>X1</b>     | 0                | <b>X1</b>     | 1                | $\mathbf{X0}$ | 0              | <b>X1</b>     |

| 1              | 1     | 0                     | 1                | $\mathbf{X0}$ | 1                | $\mathbf{X0}$ | 0                | <b>X1</b>     | 0              | <b>X1</b>     |

| $\mathbf{y}_3\mathbf{X}_2$                  |    |    |    | $\overline{\mathbf{X}_{1}} =$ | 0  |

|---------------------------------------------|----|----|----|-------------------------------|----|

| <b>y</b> <sub>1</sub> <b>y</b> <sub>2</sub> |    | 00 | 01 | 11                            | 10 |

|                                             | 00 | 1  | 1  | 1                             | 0  |

|                                             | 01 | X  | X  | X                             | X  |

|                                             | 11 | X  | X  | X                             | X  |

|                                             | 10 | X  | X  | X                             | X  |

| $y_3X_2$ $y_1y_2$ | 2 | $X_1 = 1$ |   |   |  |

|-------------------|---|-----------|---|---|--|

| J 1 J 2           | 0 | 0         | 0 | 1 |  |

|                   | X | X         | X | X |  |

|                   | X | X         | X | X |  |

|                   | X | X         | X | X |  |

$$J_2 = X_1 y_3 \overline{X_2} + \overline{X_1} \overline{y_3} + \overline{X_1} X_2$$

$$y_3 X_2$$

$y_1 y_2$

$X X X X X$

$X X 1 0$

$0 0 1 1 1$

| $y_1y_2$ | 2 |   |   |   |

|----------|---|---|---|---|

| 00       | X | X | X | X |

| 01       | X | X | 1 | 1 |

| 11       | 1 | 1 | 1 | 0 |

| 10       | X | X | X | X |

$$K_2 = y_3 X_2 + \overline{y_1} y_2 X_1 + X_2 \overline{y_3} + \overline{X_1} y_3 y_1$$

|                | ( <b>P.S</b> ) |                       |                | $_{1}$ $X_{2}$ |                |               |                |               |                |           |

|----------------|----------------|-----------------------|----------------|----------------|----------------|---------------|----------------|---------------|----------------|-----------|

|                |                |                       |                | 00             |                | 01            |                | 10            |                | 11        |

| $\mathbf{y_1}$ | $y_2$          | <b>y</b> <sub>3</sub> | $\mathbf{Y}_3$ | $J_3K_3$       | $\mathbf{Y}_3$ | $J_3K_3$      | $\mathbf{Y}_3$ | $J_3K_3$      | $\mathbf{Y}_3$ | $J_3K_3$  |

| 0              | 0              | 0                     | 1              | 1X             | 1              | 1X            | 0              | <b>0X</b>     | 0              | 0X        |

| 0              | 0              | 1                     | 1              | $\mathbf{X0}$  | 1              | $\mathbf{X0}$ | 1              | $\mathbf{X0}$ | 0              | <b>X1</b> |

| 0              | 1              | 1                     | 1              | $\mathbf{X0}$  | 1              | $\mathbf{X0}$ | 0              | <b>X1</b>     | 0              | <b>X1</b> |

| 1              | 1              | 1                     | 1              | $\mathbf{X0}$  | 0              | <b>X1</b>     | 1              | $\mathbf{X0}$ | 0              | <b>X1</b> |

| 1              | 1              | 0                     | 0              | $\mathbf{0X}$  | 0              | $\mathbf{0X}$ | 0              | $\mathbf{0X}$ | 0              | 0X        |

| $y_3X_2$ $y_1y_2$ |   |   | $X_1 =$ | 0 |

|-------------------|---|---|---------|---|

|                   | 1 | 1 | X       | X |

|                   | X | X | X       | X |

|                   | 0 | 0 | X       | X |

|                   | X | X | X       | X |

| $y_3X$ $y_1y_2$ | -2 |   | $X_1 =$ | :1 |

|-----------------|----|---|---------|----|

|                 | 0  | 0 | X       | X  |

|                 | X  | X | X       | X  |

|                 | 0  | 0 | X       | X  |

|                 | V  | v | V       | V  |

$$J_3 = \overline{X_1} \overline{y_1}$$

| y <sub>3</sub> X | 2 |   |   |   |

|------------------|---|---|---|---|

| $y_1y_2$         | X | X | 1 | 0 |

|                  | X | X | 1 | 1 |

|                  | X | X | 1 | 0 |

|                  | X | X | X | X |

$$K_3 = X_2 y_1 + X_1 X_2 + X_1 \overline{y_1} y_2$$

| $y_3X$ $y_1y_2$ | -2 | $\overline{\mathbf{X}_{1}}$ | =0 |   |

|-----------------|----|-----------------------------|----|---|

| J 1 J 2         | 0  | 0                           | 0  | 1 |

|                 | X  | X                           | 0  | 0 |

|                 | 0  | 0                           | 0  | 1 |

|                 | X  | X                           | X  | X |

| y <sub>3</sub> y | $\zeta_2$ | $X_1 = 1$ |   |   |  |  |

|------------------|-----------|-----------|---|---|--|--|

| $y_1y_2$         | 0         | 0         | 0 | 1 |  |  |

|                  | X         | X         | 0 | 0 |  |  |

|                  | 0         | 0         | 0 | 1 |  |  |

|                  | X         | X         | X | X |  |  |

$$Z=y_1y_3\overline{X_2}+\overline{y_2}y_3\overline{X_2}$$

## **Example**

Design a sequential logic circuit to detect the sequence (111) whenever occur. Draw the circuit. Using T-F.F.

Design a sequential logic circuit under the following condition:

1) The circuit will get O/P (1) for every Group of four pulses that starts with zero and ends at (1) but the second bit is the similar to third bit.

عنوان البريد الاليكتروني

- 2) The analysis of the first group, which will began when it is starts the first zero in the sequence of input.

- 3) The analysis of the next group will not start until the end of the group of four pulses whether it provides an output or not.

- 4) Use any F.F in the design.

# **Lectures of Electrical Engineering Department**

Subject Title: Digital Electronics

Class: 3rd Electronics

|          | Lecture sequences:                                                                                                       | Fifth lecture                 | Instructor Name    | :            |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------|--------------|--|--|--|

|          | The major contents:                                                                                                      |                               |                    |              |  |  |  |

|          | 1-Function Implementation Using PLD'S                                                                                    |                               |                    |              |  |  |  |

|          | 2-Types of PLD'S                                                                                                         |                               |                    |              |  |  |  |

|          | 3-Design of PLD'S                                                                                                        |                               |                    |              |  |  |  |

|          |                                                                                                                          |                               |                    |              |  |  |  |

|          | The detailed contents:                                                                                                   |                               |                    |              |  |  |  |

|          | 1- Function Implem                                                                                                       | entation Using PLD'           | <u>s</u>           |              |  |  |  |

|          | PLD'S: Programmable Log                                                                                                  | ic Devices.                   |                    |              |  |  |  |

|          | PLD'S: A logic devices is one in which the logic function is programmed by In some cases can be reprogrammed many times. |                               |                    |              |  |  |  |

| Lecture  |                                                                                                                          |                               |                    |              |  |  |  |

| Contents |                                                                                                                          |                               |                    |              |  |  |  |

|          | 2-Types of PLD'S                                                                                                         |                               |                    |              |  |  |  |

|          | 1- <b>SPLD</b> : (Simple PI                                                                                              | LD) are the least complex for | m of PLD'S. The ca | ategories of |  |  |  |

|          | SPLD'S are:                                                                                                              |                               |                    |              |  |  |  |

|          | PAL: (Programm                                                                                                           | able Array Logic).            |                    |              |  |  |  |

|          | GAL: (Generic A                                                                                                          | rray Logic)                   |                    |              |  |  |  |

|          | PLA: (Programm                                                                                                           | able Logic Array)             |                    |              |  |  |  |

|          | <b>PROM:</b> (Progran                                                                                                    | nmable Read-only Memory)      |                    |              |  |  |  |

|          | 2- <b>CPLD:</b> (Complex                                                                                                 | PLD) have a much higher ca    | apacity than SPLD, | Permitting   |  |  |  |

|          | more complex log                                                                                                         | ic circuits to be programmed  | into them.         |              |  |  |  |

|          | 3- <b>FPGAs:</b> (Filed P                                                                                                | rogrammed Gate Arrays) a      | re different from  | SPLD and     |  |  |  |

CPLD.

**FPGAs:** Consists of an array of anywhere from 64 to thousands of logic gate groups.

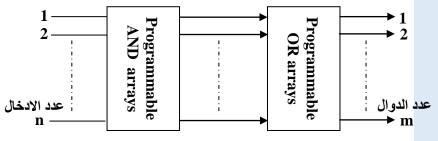

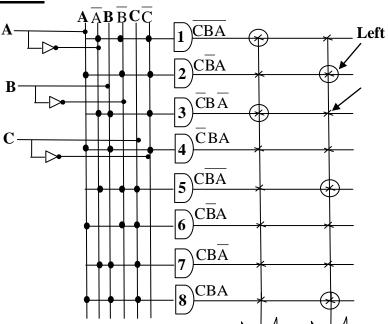

# **PLA**

Is an "SPLD" that consists of a <u>programmable "AND" array</u> and programmable "OR" arrays.

The PLA is called an (FPLA) (Filed Programmable Logic Array) because the user is the field not the manufacture programs it.

#### **PROM**

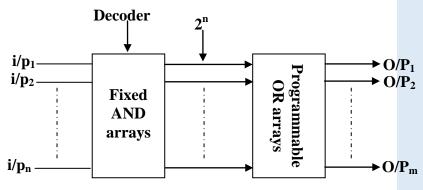

**Block Diagram of a PLA**

Consists of a set of fixed (non programmable) AND gates connected as a decoder and programmable OR arrays. Each AND gate has "n" inputs and each OR gate has (2<sup>n</sup>) inputs. The no. of OR gates is equal to the word size (m) that stored in memory.

no. of AND =  $2^n$

**Block Diagram of a PROM**

no. of input of each AND = n

no. of OR = no. of word size = m

no. of input in each OR gate = no. of AND gate

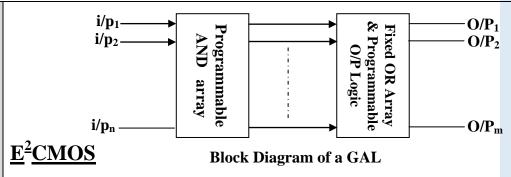

### **GAL**

Has a reprogrammable AND array and a fixed OR array with programmable O/P logic. The <u>two main</u> differences between GAL and PAL devices are (a) GAL is reprogrammable (b) GAL has programmable output.

The GAL can be reprogrammed again and again because it uses E<sup>2</sup>CMOS technology instead of <u>bipolar technology</u> and fusible links.

Electrically erasable complementary metal oxide semiconductor.

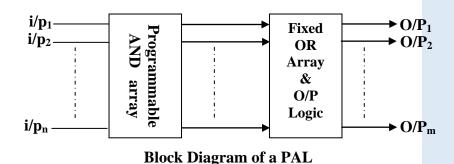

#### **PAL**

A PAL is an SPLD that was developed to overcome certain disadvantages of the PLA, such as <u>longer-delays</u> due to the additional fusible links that result from using two programmable arrays and <u>more</u> circuit complexity but is not as flexible as the PLA. The PAL is the most common one-time programmable (OTP) logic device and is implemented with bipolar technology (TTL or ECL).

**ECL:** Emitter Coupled Logic.

TTL: Transistor Transistor Logic.

increment its digital O/P from one <u>Code to</u> the Next <u>higher code</u>. An n-bit ADC can resolve one part in (2<sup>n</sup>-1). It may be expressed as a percentage of full scale or in bits. The resolution of 8-bit ADC can be expressed as one part in 256 or as 0.39% of full scale or simply as 8-bit resolution.

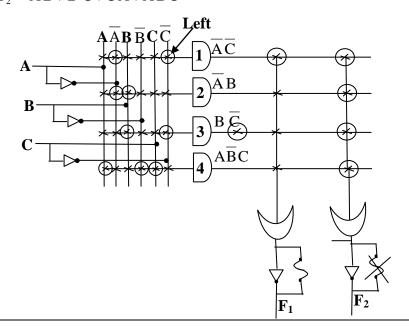

#### 3- Example

Implement the following functions by using (1) PROM (2) PLA technique (AND-OR-NOT).

$$F_1 = \sum 0, 2, \quad F_2 = \sum 1, 4, 7$$

# **Solution**

- (\*) Indicates a hard-wired interconnection.

- (x) Indicates an intact (or unprogrammed) fusible link or interconnection.

#### 1) PROM

By Using PLA Technique:

| $\mathbf{F_1}$ | PLA Program Table |

|----------------|-------------------|

|                |                   |

| 1              |                   |

| BA<br>C | 00 | 01 | 11 | 10 |

|---------|----|----|----|----|

| 0       | 1  | 0  | 0  | 1  |

| 1       | 0  | 0  | 0  | 0  |

|         | _  |    |    |    |

| $C^{BA}$ | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 0        | 0  | 1  | 0  | 0  |

| 1        | 1  | 0  | 1  | 0  |

|          |    |    |    |    |

$$F_{1} = \overline{A}\overline{C} \qquad F_{2} = A\overline{B}\overline{C} + \overline{A}\overline{B}C + ABC$$

$$\overline{F_{1}} = A + C \qquad \overline{F_{2}} = \overline{A}B + B\overline{C} + \overline{C}\overline{A} + A\overline{B}C$$

| Pro          | duct           | Inputs |   |   | Out            | <u>puts</u> |  |

|--------------|----------------|--------|---|---|----------------|-------------|--|

| te           | rm             | C      | В | A | $\mathbf{F_1}$ | $F_2$       |  |

| Ā            | $\overline{C}$ | 0      | - | 0 | 1              | 1           |  |

| Ā            | В              | -      | 1 | 0 | •              | 1           |  |

| В            | $\overline{C}$ | 0      | 1 | - | -              | 1           |  |

| $\mathbf{A}$ | В С            | 1      | 0 | 1 | -              | 1           |  |

|              |                |        |   |   |                |             |  |

#### **Example**

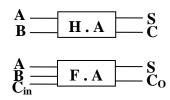

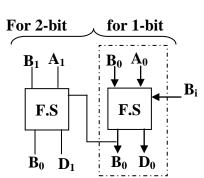

Show the logic arrangement of PLA (AND-OR) required to implement binary full adder.

0

| ABC | 00 | 01 | 11 | 10 |

|-----|----|----|----|----|

| 0   | 0  | 1  | 0  | 1  |

| 1   | 1  | 0  | 1  | 0  |

$$S = \overline{ABC}_{i} + \overline{ABC}_{i} + A\overline{BC}_{i} + ABC_{i}$$

$$\overline{S} = \overline{ABC}_{i} + A\overline{BC}_{i} + \overline{ABC}_{i} + AB\overline{C}_{i}$$

| A | В | $C_{in}$ | $S_{m}$ | $\mathbf{C_0}$ | <b>B</b> |

|---|---|----------|---------|----------------|----------|

| 0 | 0 | 0        | 0       | 0              | A `      |

| 0 | 0 | 1        | 1       | 0              | 9        |

| 0 | 1 | 0        | 1       | 0              | ]        |

| 0 | 1 | 1        | 0       | 1              |          |

| ABC |   | 01 | 11 | 10 |

|-----|---|----|----|----|

| 0   | 0 | 0  | 1  | 0  |

| 1   | 0 | 1  | 1  | 1  |

$$C_o = AC_i + AB + BC_i$$

$$\overline{C_o} = \overline{A}\overline{B} + \overline{B}\overline{C_i} + \overline{B}\overline{C_i}$$

$$PLA (AND - OR - NOT) \longleftarrow F$$

$$PLA (AND - OR) \longleftarrow F$$

| Product        |                         |                              | I | nput | ts      | Outputs      |                |

|----------------|-------------------------|------------------------------|---|------|---------|--------------|----------------|

|                | ???                     |                              | A | В    | $C_{i}$ | $\mathbf{S}$ | $\mathbf{C_o}$ |

| $\overline{A}$ | $\overline{\mathrm{B}}$ | Ci                           | 0 | 0    | 1       | 1            | -              |

| Ā              | В                       |                              | 0 | 1    | 0       | 1            | -              |

| A              | $\overline{B}$          | $\frac{\overline{C_i}}{C_i}$ | 1 | 0    | 0       | 1            | -              |

| $\mathbf{A}$   | B                       | $\mathbf{C_i}$               | 1 | 1    | 1       | 1            | -              |

| A              | $C_{i}$                 |                              | 1 | -    | 1       | -            | 1              |

| $\mathbf{A}$   | В                       |                              | 1 | 1    | -       | -            | 1              |

| В              | $C_{i}$                 |                              | - | 1    | 1       | -            | 1              |

**PLA Program Table**

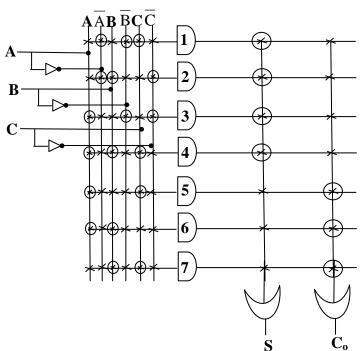

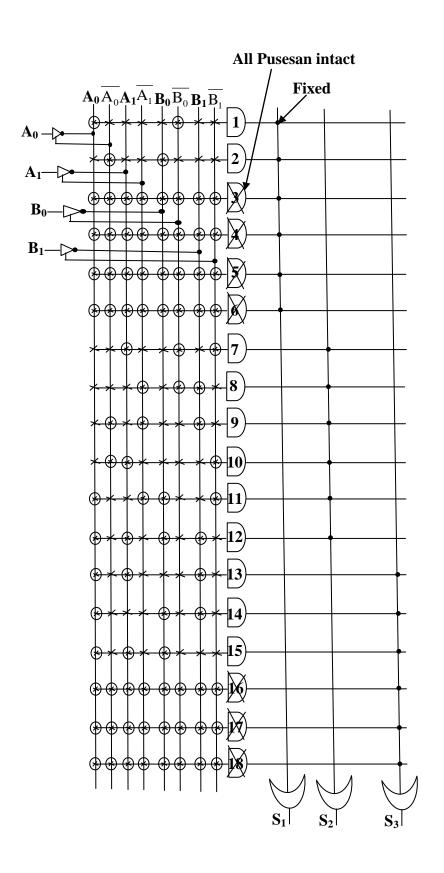

Construct a large circuit using PLA (AND-OR-NOT) and PAL that adds two binary numbers (A and B). Each binary number is composed of two bits (i.e. A =

| $\mathbf{A}_1\mathbf{A}_0,\mathbf{B}=\mathbf{B}_1\mathbf{B}_0)$ | , |

|-----------------------------------------------------------------|---|

|-----------------------------------------------------------------|---|

**Example**

| $\mathbf{B_1}$ | $\mathbf{B_0}$ | $\mathbf{A_1}$ | $\mathbf{A_0}$ | $S_3$ | $S_2$ | $S_1$ |

|----------------|----------------|----------------|----------------|-------|-------|-------|

| 0              | 0              | 0              | 0              | 0     | 0     | 0     |

| 0              | 0              | 0              | 1              | 0     | 0     | 1     |

| 0              | 0              | 1              | 0              | 0     | 1     | 0     |

| 0              | 0              | 1              | 1              | 0     | 1     | 1     |

| 0              | 1              | 0              | 0              | 0     | 0     | 1     |

| 0              | 1              | 0              | 1              | 0     | 1     | 0     |

| 0              | 1              | 1              | 0              | 0     | 1     | 1     |

| 0              | 1              | 1              | 1              | 1     | 0     | 0     |

| 1              | 0              | 0              | 0              | 0     | 1     | 0     |

| 1              | 0              | 0              | 1              | 0     | 1     | 1     |

| 1              | 0              | 1              | 0              | 1     | 0     | 0     |

| 1              | 0              | 1              | 1              | 1     | 0     | 1     |

| 1              | 1              | 0              | 0              | 0     | 1     | 1     |

| 1              | 1              | 0              | 1              | 1     | 1     | 0     |

| 1              | 1              | 1              | 1              | 1     | 0     | 1     |

| 1              | 1              | 1              | 1              | 1     | 1     | 0     |

| $A_1A_0$ | )  |    |    |    |

|----------|----|----|----|----|

| $B_1B_0$ | 00 | 01 | 11 | 10 |

| 00       | 0  | 0  | 0  | 0  |

| 01       | 0  | 0  | 1  | 0  |

| 11       | 0  | 1  | 1  | 1  |

| 10       | 0  | 0  | 1  | 1  |

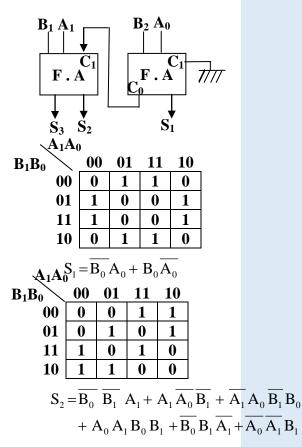

$$S_3 = B_1 A_1 + A_0 A_1 B_0 + B_0 B_1 A_0$$

[o. of AND gate = no. of outputs \* max. product terms in the logic equation for the output =  $3 \times 6 = 18$

#### **PAL Program table**

| Dwa | Product terms                                                            |                | AND              | i/pS           |                | Outnut                                                       |

|-----|--------------------------------------------------------------------------|----------------|------------------|----------------|----------------|--------------------------------------------------------------|

| Pro | duct terms                                                               | $\mathbf{B_1}$ | $\mathbf{B}_{0}$ | $\mathbf{A_1}$ | $\mathbf{A_0}$ | Output                                                       |

| 1.  | $\overline{\mathbf{B}_0} \ \mathbf{A_0}$                                 | -              | 0                | -              | 1              |                                                              |

| 2.  | $\mathbf{B_0} \qquad \overline{\mathbf{A}_0}$                            | -              | 1                | -              | 0              |                                                              |

| 3.  |                                                                          | -              | -                | -              | -              | $S = \overline{B_0} A_0 + B_0 \overline{A_0}$                |

| 4.  |                                                                          | -              | -                | -              | -              | ~ -0000                                                      |

| 5.  |                                                                          | -              | -                | -              | -              |                                                              |

| 6.  |                                                                          | -              | -                | -              | -              |                                                              |

| 7.  | $\mathbf{A_1}  \mathbf{B_0}  \mathbf{B_1}$                               |                | 0                | 1              | -              | $S_2 = A_1 \overline{B_0} \overline{B_1} +$                  |

| 8.  | $\mathbf{B_1}  \mathbf{B_0}  \mathbf{A_1}$                               | 1              | 0                | 0              | -              | $B_1 \overline{B_0} A_1 + \overline{A_0} \overline{A_1} B_1$ |

| 9.  | $\overline{\mathbf{A}}_{0} \ \overline{\mathbf{A}}_{1} \ \mathbf{B}_{1}$ |                | -                | 0              | 0              |                                                              |

| 10. | $A_1 A_0 \overline{B_1}$                                                 | 0              | -                | 1              | 0              | $+A_1A_0B_1+A_0A_1B_0B_1$                                    |

| 11. | $\mathbf{A_0} \mathbf{A_1} \mathbf{B_0} \mathbf{B_1}$                    | 0              | 1                | 0              | 1              | $+ \mathbf{A}_0  \mathbf{A}_1  \mathbf{B}_0  \mathbf{B}_1$   |

| 12. | $A_0A_1B_0\ B_1$                                                         | 1              | 1                | 1              | 1              |                                                              |

| 13. | $\mathbf{B_1}$ $\mathbf{A_1}$                                            | 1              | -                | 1              | -              |                                                              |

| 14. | $\mathbf{B_0}  \mathbf{B_1}  \mathbf{A_1}$                               | 1              | 1                | -              | 1              | $S_3 = B_1 A_1$                                              |

| 15. | $A_0 A_1 B_0$                                                            | -              | 1                | 1              | 1              | $+B_0B_1A_0$                                                 |

| 16. |                                                                          | -              | -                | -              | -              | 0 1 0                                                        |

| 17. |                                                                          | -              | -                | -              | -              | $+\mathbf{A}_0\mathbf{A}_1\mathbf{B}_0$                      |

| 18. |                                                                          | -              | -                | -              | -              |                                                              |

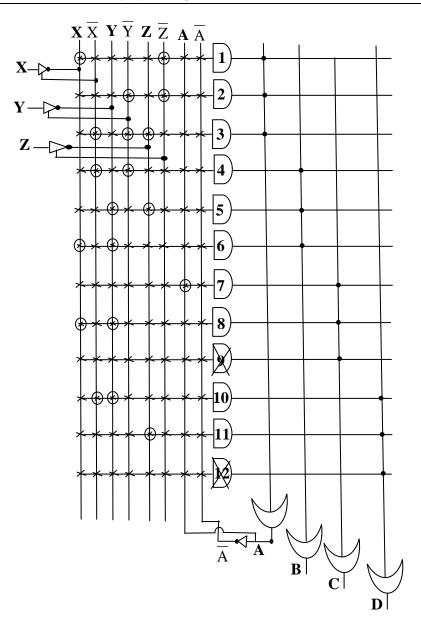

# **Example**

Use PAL to implement the following functions:

$$A(x,y,z) = \sum (1,2,4,6)$$

$$B(x,y,z) = \sum (0,1,3,6,7)$$

$$C(x,y,z) = \sum (1,2,4,6,7)$$

$$D(x, y, z) = \sum (1, 2, 3, 5, 7)$$

After using K – map, the equations for the outputs will be as following:

$$A = \left( X\overline{Z} + Y\overline{Z} + \overline{X}\,\overline{Y}\,Z \right)$$

$$B = \left(\overline{X} \, \overline{Y} + YZ + XY\right)$$

$$C = (X\overline{Z} + Y\overline{Z} + \overline{X}\overline{Y}Z + XY) \Rightarrow C = A + XY$$

$$D = \left(\overline{X} Y + Z\right)$$

#### **Program PAL Table**

| Duo | duct terms                           |   | Inj | put |   | Outnut                                    |  |  |

|-----|--------------------------------------|---|-----|-----|---|-------------------------------------------|--|--|

| Pro | duct terms                           | X | Y   | Z   | A | Output                                    |  |  |

| 1.  | $\mathbf{X} \overline{\mathbf{Z}}$   | 1 | -   | 0   | - |                                           |  |  |

| 2.  | $\mathbf{Y} \ \overline{\mathbf{Z}}$ | - | 1   | 0   | - | A = XZ + YZ + XYZ                         |  |  |

| 3.  | $\overline{X}$ $\overline{Y}$ $Z$    | 0 | 0   | 1   | - |                                           |  |  |

| 4.  | $\overline{X}$ $\overline{Y}$        | 0 | 0   | -   | - |                                           |  |  |

| 5.  | Y Z                                  | - | 1   | 1   | - | $B = \overline{X} \overline{Y} + YZ + XY$ |  |  |

| 6.  | XY                                   | 1 | 1   | -   | - |                                           |  |  |

| 7.  | A                                    | - | -   | -   | 1 |                                           |  |  |

| 8.  | XY                                   | 1 | 1   | -   | - | C=A+XY                                    |  |  |

| 9.  |                                      | - | -   | -   | - |                                           |  |  |

| 10. | $\overline{\overline{X}}$ Y          | 0 | 1   | -   | - |                                           |  |  |

| 11. | $\mathbf{Z}$                         | - | -   | 1   | - | $D = \overline{X}Y + Z$                   |  |  |

| 12. |                                      | - | -   | -   | - |                                           |  |  |

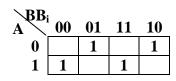

#### **Full Substructure**

| A | В | B <sub>i</sub> | D | $\mathbf{B_0}$ |

|---|---|----------------|---|----------------|

| 0 | 0 | 0              | 0 | 0              |

| 0 | 0 | 1              | 1 | 1              |

| 0 | 1 | 0              | 1 | 1              |

| 0 | 1 | 1              | 0 | 1              |

| 1 | 0 | 0              | 1 | 0              |

| 1 | 0 | 1              | 0 | 0              |

| 1 | 1 | 0              | 0 | 0              |

| 1 | 1 | 1              | 1 | 1              |

$$D = A\overline{B} \overline{B_1} + \overline{AB}B_i + ABB_i + \overline{ABB_i}$$

$$B_o = \overline{AB} + \overline{AB}B_i + BB_i$$

| ABB <sub>i</sub> | 00 i | 01 | 11 | 10 |

|------------------|------|----|----|----|

| 0                |      | 1  | 1  | 1  |

| 1                |      |    | 1  |    |

|                  |      |    |    |    |

$$B_0 = \overline{A}B + \overline{A}B_i + BB_i$$

| جامعة الموصل/ كلية الهندسة |  |

|----------------------------|--|

|                            |  |

|                            |  |

|                            |  |

|                            |  |

|                            |  |

|                            |  |

|                            |  |

|                            |  |

|                            |  |

|                            |  |

|                            |  |

|                            |  |

|                            |  |

|                            |  |

|                            |  |

|                            |  |

|                            |  |

|                            |  |

|                            |  |