# **Lectures of Electrical Engineering Department**

Subject Title: Microelectronics

Class: 4th Electronic and Communications

|                     | Lecture sequences:     | First lecture | Instructor Name | : |

|---------------------|------------------------|---------------|-----------------|---|

|                     | The major contents:    |               |                 |   |

|                     | 1- Tunnel Diode        |               |                 |   |

|                     | 2-                     |               |                 |   |

|                     | 3-                     |               |                 |   |

| Lecture<br>Contents | 4-                     |               |                 |   |

|                     |                        |               |                 |   |

|                     | The detailed contents: |               |                 |   |

|                     | 1- Working principle   |               |                 |   |

|                     | 2- Characteristics     |               |                 |   |

|                     | 3- Applications        |               |                 |   |

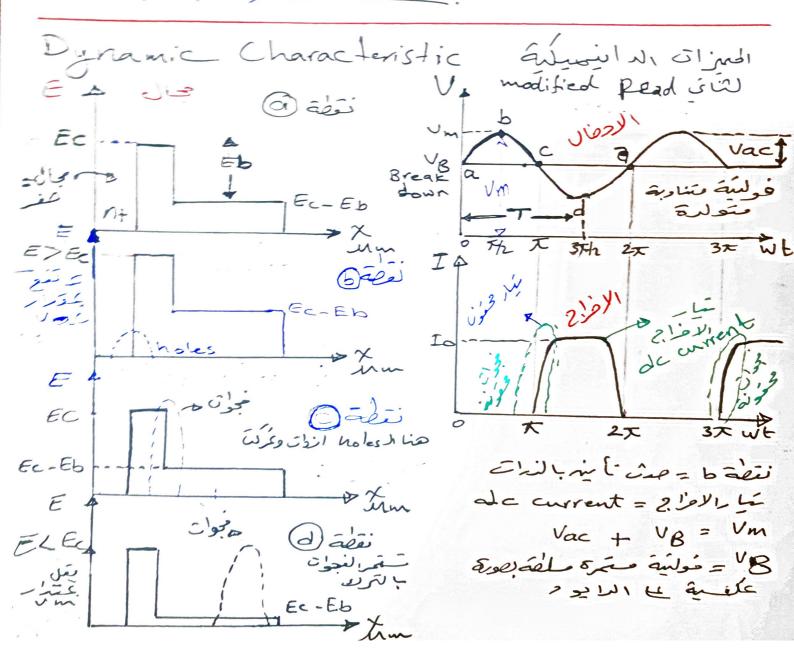

(न्याम) अद्या गंम दं क्यां पंच L بأسر التفايل أو التناظر به منطقة ( سُمْ على المنافر طامل مِنْ ع وعشها سوريم عمله تنفيه التقال ما للالكريات سرائة المفقة م الحالت إلم عه: ا) المنفقة ٦ مبالنايي صون شدله ك الرين، عن مخ barrier 4 Imax of IP PU = V2 حنان عند الحالة والراعم) ، تعامله النولية المطفة الأنكاه لإمامي V3 6= 31 V/2 mes / rice الساعة (الأندة) ١٠ رشعن الأعلى me is a sie 1 Epp n Lieuis الحالة الا عمر (النالية) المعنف ربالتالي ما تنفذ ما المفات ا (dialidian) backing نتيجة زارة التدلسة بأم مراجه الحامر سن يس أبها مناك علاقفية مرات برسي م رط سعف میں کر منبقص سببالتا ہی نا ہر ، دسیار سنے عیل کھٹا لأسمعاس التنفيس قلة عدالساس

الرطف الخامية I,=I3 EFP RYNY WITH PDI AV V=Va صناع جده الحالة (الخامة) ، نتوم بزارة صنا حد التيار العولية المسلفة بالانجاء الإنامي عدار in ceivi m si cui ; Efn n l'ép si (1 (V=0) m のりしいだしいからり فيكد منية عين رندلای ما « EFP ، ای مان س سُعِلْمَهُ مِي النَّالِي ٱلمنتَّقِي very (, ales 1, in U \ ald 1 ouent a féer a costilles بالأعاه الأساعي الم عد المنطقة ط الم تنا فرسنما) دبنغرالوثث سوت تمر (تنخم) الالكرمات دكندلك نشيمة زيارة الغولسم بالرياه Parei un aeli m الامات خار انبه الحا جرسمة بعد عدة المرفلة أوالحالث mit de أد بعد هذه النامة ربالنشيخ کا ۱ لک رسعن ميل حنار بالتاني النق عَنْ عَمْ مَا رَافًا ا نش المنائي الماعيادي دلانوهد أي وجور لعمله ا ي يكه مو مداليا lunnding o, Liet till, in ill il. مُعامِ النَّاي / عسادي

الرملة المسادمين PDn TV V= 5 = 0.6,1 0.7 - 20121 sie ino عنها: يبدأ السّار الحراري بالتناصيب لعود خولية الاتماز = خولية الحام للثنائ IA Thermal Convent Iv= Current Vollan سُار العادي أم at V=/v - o I funnels år i ne rædd QU = V4 IThrone Ju - Voltage Valley المغدلسة التي عنرها يلوس المنار الحرب على المنار المنار الحرب عن المنار المنار الحرب المنار العادا العادمة حالة عند السار العادمة العادمة لأبه السّاء الرعسّادي أو السّاري صابح الشّاتي العادي (Thermal) 5-1-1-1-10, is رهن نکوس المفادم لے دھي موسم في مس ن على السكر النفي يكور معلوسي خسانا ، لاء إلى الم رفقائة شا غفا ا aidid oiem slier (án La ar led!) Amplifiers Descillators Third Je ? at V=VV = I Tunnel = I Thermal

# **Lectures of Electrical Engineering Department**

# Subject Title: Microelectronics

# Class: 4th Electronic and Communications

|                                 | Lecture sequences:                                  | First lecture | <b>Instructor Name</b> | • |

|---------------------------------|-----------------------------------------------------|---------------|------------------------|---|

|                                 | The major contents:                                 |               |                        |   |

|                                 | 1- Basic Concepts                                   |               |                        |   |

|                                 | 2- Types of Solids (Conductivity)                   |               |                        |   |

| 3- Types of Solids (Structures) |                                                     |               |                        |   |

|                                 | 4-                                                  |               |                        |   |

| Lecture Contents                |                                                     |               |                        |   |

|                                 | The detailed contents:  1- Semiconductors Materials |               |                        |   |

|                                 |                                                     |               |                        |   |

|                                 | 2- Atomic structure                                 |               |                        |   |

|                                 | 3- ENERGY BAND                                      |               |                        |   |

|                                 | 4- Diffusion Current Density                        |               |                        |   |

|                                 |                                                     |               |                        |   |

1

# **Basic Concepts**

# Types of Materials:

- 1-Solids.

- 2-Liquids.

- 3-Gases.

# Types of Solids (Conductivity):

# Types of Solids (Structures):

- 1- Insulators.

- 2- Semiconductors.

- 3- Conductors.

- 1- Amorphous.

- 2- Polycrystalline.

- 3- Single crystalline.

#### **Semiconductors Materials:**

The conductivity of a semiconductor is generally sensitive to temperature, illumination, magnetic field, and minute amounts of impurity atoms. This sensitivity in conductivity makes the semiconductor one of the most important materials for electronic applications.

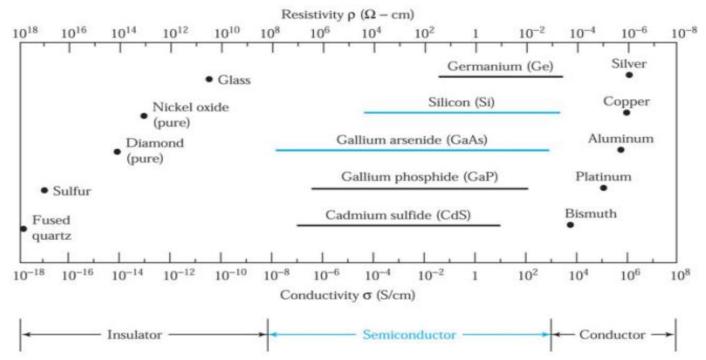

Figure 1 shows the range of electrical conductivities  $\sigma = S/cm$  and resistivities  $\rho = 1/\sigma$

Fig. 1 Typical range of conductivities for insulators, semiconductors, and conductors.

$$S = 1/\Omega$$

,  $\rho = cm * \Omega$   $\rho = Rho$  ,  $\sigma = Sigma$  ,  $S = Siemens$

#### **Element Semiconductors**

In the early 1950s, germanium was the major semiconductor material. Since the early 1960s silicon has become a practical substitute and has now virtually supplanted germanium as a semiconductor material. The main reasons we now use silicon are that silicon devices exhibit better properties at room temperature (teeny leakage current) and (high-quality silicon dioxide can be grown thermally).

| Period | Column II | III      | IV        | V          | VI        |

|--------|-----------|----------|-----------|------------|-----------|

| 2      |           | В        | С         | N          | 0         |

|        |           | Boron    | Carbon    | Nitrogen   | Oxygen    |

| 3      | Mg        | Al       | Si        | P          | S         |

|        | Magnesium | Aluminum | Silicon   | Phosphorus | Sulfur    |

| 4      | Zn        | Ga       | Ge        | As         | Se        |

|        | Zinc      | Gallium  | Germanium | Arsenic    | Selenium  |

| 5      | Cd        | In       | Sn        | Sb         | Te        |

|        | Cadmium   | Indium   | Tin       | Antimony   | Tellurium |

| 6      | Hg        |          | Pb        |            |           |

|        | Mercury   |          | Lead      |            |           |

# **Compound Semiconductors**

In recent years a number of compound semiconductors have found applications for various devices. A binary compound is a combination of two elements from the periodic table.

Many of the compound semiconductors have electrical and optical properties that are different from those of silicon. These semiconductors, especially GaAs, are used mainly for high-speed electronic, microwave and photonic applications.

| Elemental | IV compounds | Binary III-V compounds | Binary II-VI compounds |

|-----------|--------------|------------------------|------------------------|

| Si        | SiC          | AlP                    | ZnS                    |

| Ge        | SiGe         | AlAs                   | ZnSe                   |

|           |              | AlSb                   | ZnTe                   |

|           |              | GaP                    | CdS                    |

|           |              | GaAs                   | CdSe                   |

|           |              | GaSb                   | CdTe                   |

# Atomic structure

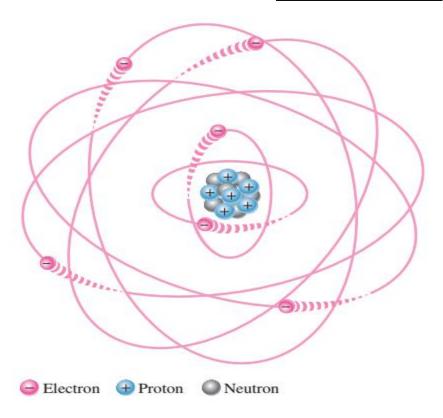

The Bohr model of an atom showing electrons in circular orbits around the nucleus. The "tails" on the electrons indicate they are moving.

Mass of (Neuton or Proton) =  $1.66*10^{-27}Kg$ Mass of Electron  $< 1800 \ time$  of  $\ proton \ mass$

< 1800 time of neutron mass

Energy levels increase as the distance from the nucleus increases.

Electon Energy (E<sub>H</sub>) =  $\frac{-13.6}{n^2} ev$

An electron–volt is the energy of an electron that has been accelerated through a potential difference of 1 volt, and 1 eV =  $1.6 \times 10$ -19 joules.

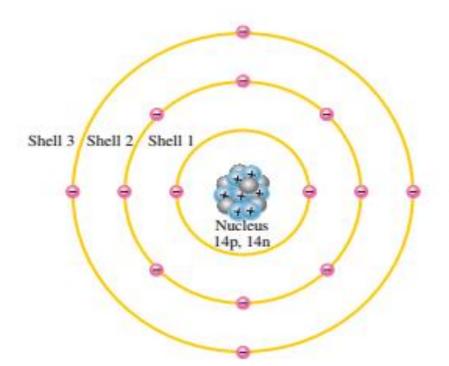

#### **Electron Shells and Orbits**

Electrons orbit of an atom at certain distances from the nucleus. Electrons near the nucleus have less energy than those in more distant **orbits**.

Each orbit from the nucleus corresponds to a certain energy level . In an atom, the orbits are grouped into energy bands known as **shells**.

#### **Valence Electrons**

Electrons that are in orbits farther from the nucleus have higher energy and are less tightly bound to the atom than those closer to the nucleus. Electrons with the highest energy levels exist in the outermost shell of an atom and are loosely bound to the atom. This outermost shell is known as the **valance** shell, and electrons in this shell are called **valence electrons**. The chemical activity of a material is determined primarily by the number of such electrons.

#### **Free Electrons and Ions**

If an electron absorbs a **photon** of sufficient energy, it escapes from the atom and becomes a **free electron**. Any time an atom or group of atoms acquires or loss the electron it is called an **ion**.

<u>Conductors:</u> are materials that allow current. They have a large number of free electrons and are characterized by one to three valence electrons in their structure. Most metals are good conductors. Silver is the best conductor, and copper is next.

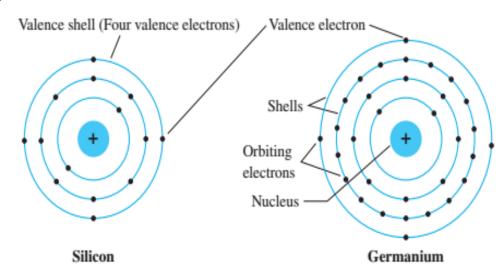

Semiconductors: are classed below the conductors in their ability to carry current because they have fewer free electrons than do conductors. Semiconductors have four valence electrons in their atomic structures. Silicon (Si), germanium (Ge) and Gallium arsenide (GaAs) are common semiconductive materials.

<u>Insulators:</u> are nonmetallic materials that are poor conductors of electric current, they are used to prevent current where it is not wanted. Insulators have no free electrons in their structure. Insulators such as glass, and Teflon.

5

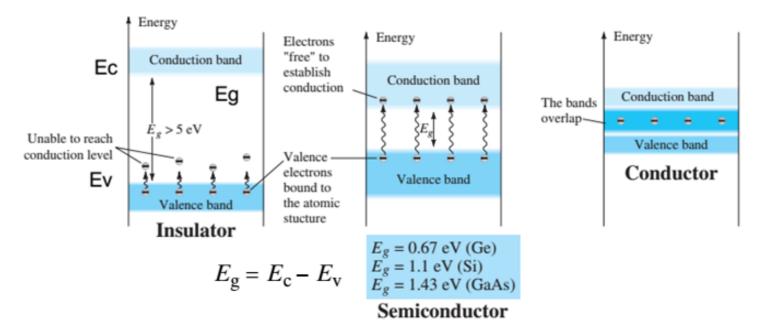

#### ENERGY BAND

<u>Valance band (Ev):</u> Is the band of electron orbitals that electrons can jump out of, moving into the conduction band when excited. The valance band is the outermost electron orbital of an atom.

Conduction band (Ec): Is the band of electron orbitals that electrons can jump up into from the valance band when excited. When the electrons are in these orbitals, they have enough energy to move freely in the material. This movement of electrons creates an electric current.

Band gap (Eg): The differnce in energy between the valance band and conduction band is called an energy gap or band gap,(Eg = Ec - Ev).

The region between these two energies is called the forbidden bandgap.

Materials that have large bandgap energies, in the range of 3 to 6 electron–volts (eV), are **insulators** because, at room temperature, essentially no free electrons exist in the conduction band.

In contrast, materials that contain very large numbers of free electrons at room temperature are **conductors**.

In a **semiconductor**, the bandgap energy is on the order of 1 eV.

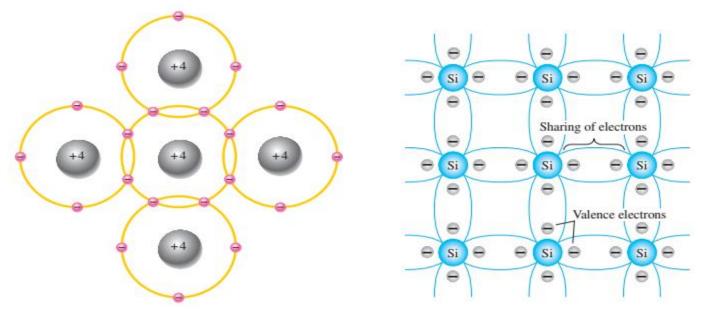

#### **Covalent Bonds**

In a pure silicon or germanium crystal the four valence electrons of one atom form a bonding arrangement with four adjoining atoms.

This bonding of atoms, strengthened by the sharing of electrons, is called covalent bonding.

Covalent bonds in silicon.

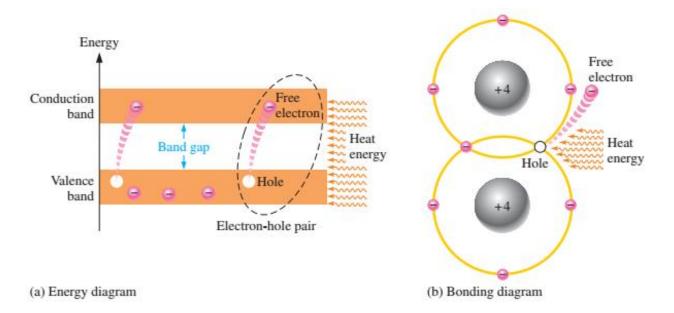

#### **Conduction Electrons and Holes**

An intrinsic (pure) silicon crystal at room temperature has sufficient heat (thermal) energy for some valence electrons to jump the gap from the valence band into the conduction band, becoming free electrons. Free electrons are also called *conduction electrons*.

7

When an electron jumps to the conduction band, a vacancy is left in the valence band within the crystal. This vacancy is called a *hole*. For every electron raised to the conduction band by external energy, there is one hole left in the valence band, creating what is called an **electron-hole pair**.

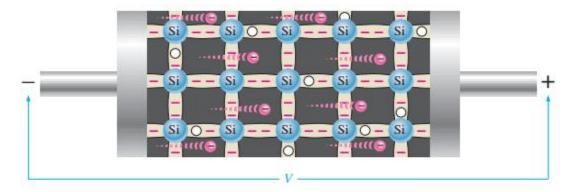

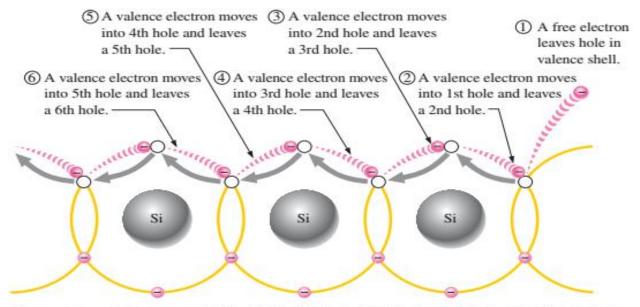

#### **Electron and Hole Current**

When a voltage is applied across a piece of intrinsic silicon, the thermally generated free electrons in the conduction band, which are free to move randomly in the crystal, are now easily attracted toward the positive end. This movement of free electrons is one type of current in a semiconductive material and is *called electron current*.

Another type of current occurs in the valence band, where the holes created by the free electrons exist. Electrons remaining in the valence band are still attached to their atoms and are not free to move randomly in the crystal structure. The hole has moved from one place to another in the crystal structure. Although current in the valence band is produced by valence electrons, it is called *hole current*.

When a valence electron moves left to right to fill a hole while leaving another hole behind, the hole has effectively moved from right to left. Gray arrows indicate effective movement of a hole.

8

#### **Intrinsic Semiconductors**

Is a single-crystal semiconductor material with no other types of atoms within the crystal. In an intrinsic semiconductor, the densities of electrons and holes are equal.

The notation  $n_i$  as the <u>intrinsic carrier concentration</u> for the concentration of the free electrons, as well as that of the holes. The equation for  $n_i$  is as follows:

$$n_i = BT^{3/2} e^{(\frac{-E_g}{2kT})}$$

where *B* is a coefficient related to the specific semiconductor material, *Eg* is the bandgap energy (eV), T is the temperature (K), *k* is Boltzmann's constant =  $(86 * 10^{-6} \text{ eV/K})$ .

| Material                | Eg (eV) | $B \text{ (cm}^{-3} \text{ K}^{-3/2})$ |  |

|-------------------------|---------|----------------------------------------|--|

| Silicon (Si)            | 1.1     | $5.23 \times 10^{15}$                  |  |

| Gallium arsenide (GaAs) | 1.4     | $2.10 \times 10^{14}$                  |  |

| Germanium (Ge)          | 0.66    | $1.66 \times 10^{15}$                  |  |

The values for B and Eg for several semiconductor materials are given

**EXAMPLE:** Calculate the intrinsic carrier concentration in silicon at T=300 K.

#### **Solution:**

$$n_i = BT^{3/2} e^{\left(\frac{-E_g}{2kT}\right)} , \quad n_i = (5.23 * 10^{15})(300)^{3/2} e^{\left(\frac{-1.1}{2(86*10^{-6})(300)}\right)}$$

$$n_i = 1.5 * 10^{10} cm^{-3}$$

Comment: An intrinsic electron concentration of  $1.5 \times 10^{10}$  cm<sup>-3</sup> may appear to be large, but it is relatively small compared to the concentration of silicon atoms, which is  $5 \times 10^{22}$  cm<sup>-3</sup>.

Intrinsic Carriers ni

| Semiconductor | Intrinsic Carriers<br>(per cubic centimeter) |  |

|---------------|----------------------------------------------|--|

| GaAs          | $1.7 \times 10^{6}$                          |  |

| Si            | $1.5 \times 10^{10}$                         |  |

| Ge            | $2.5 \times 10^{13}$                         |  |

9

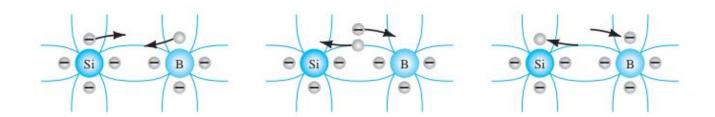

#### **Extrinsic Semiconductors**

Since the electron and hole concentrations in an intrinsic semiconductor are relatively small, only very small currents are possible. However, these concentrations can be greatly increased by adding controlled amounts of certain impurities.

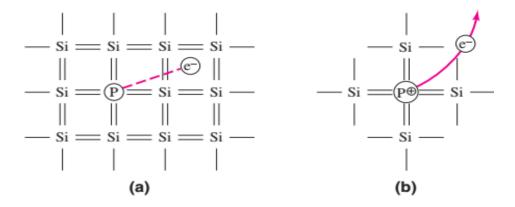

A desirable impurity is enters the crystal and replaces (i.e., substitutes for) one of the semiconductor atoms, even though the impurity atom does not have the same valence electron structure. For silicon, the desirable substitutional impurities are Boron (B) and Phosphorus (P) elements.

- (a) silicon doped with a phosphorus atom showing the fifth phosphorus valence electron

- (b) positively charged phosphorus ion after the fifth valence electron has moved into the conduction band

The phosphorus atom is called a **donor impurity**, since it donates an electron that is free to move. Although the remaining phosphorus atom has a net positive charge, the atom is immobile in the crystal and cannot contribute to the current.

Therefore, when a donor impurity is added to a semiconductor, free electrons are created without generating holes. This process is called **doping**, and it allows us to control the concentration of free electrons in a semiconductor.

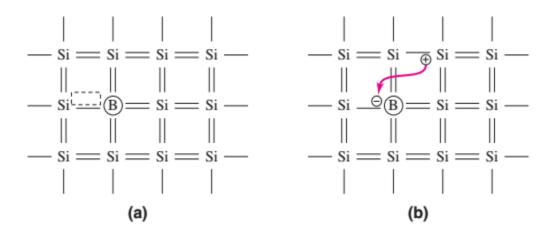

- (a) silicon doped with a boron atom showing the vacant covalent bond position

- (b) negatively charged boron ion after it has accepted an electron from the valence band.

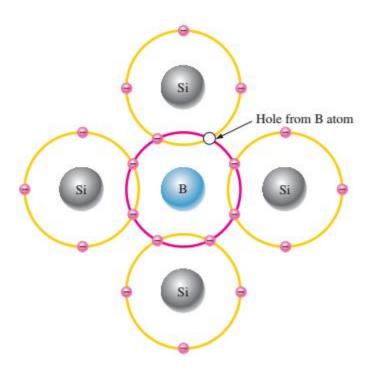

When a boron atom replaces a silicon atom, its three valence electrons are used to satisfy the covalent bond requirements for three of the four nearest silicon atoms. This leaves one bond position open.

At room temperature, adjacent silicon valence electrons have sufficient thermal energy to move into this position, thereby creating a **hole**.

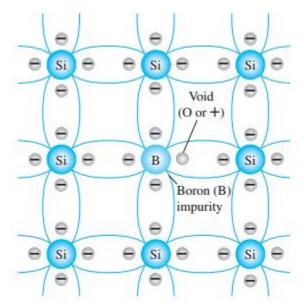

Boron impurity in p-type material.

Because the boron atom has accepted a valence electron, the boron is therefore called an **acceptor impurity.**

Acceptor atoms lead to the creation of holes without electrons being generated. This process, also called **doping**, can be used to control the concentration of holes in a semiconductor.

11

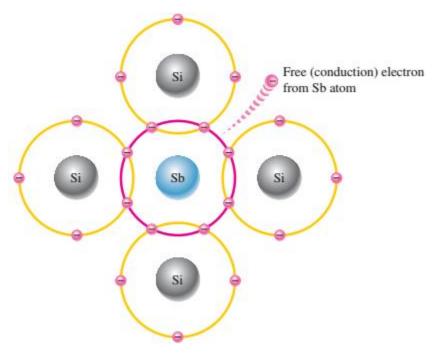

#### n-type semiconductor

To increase the number of conduction-band electrons in intrinsic silicon, **pentavalent** impurity atoms are added. These are atoms with five valence electrons such as arsenic (As),phosphorus (P), and antimony (Sb).

A semiconductor that contains donor impurity atoms is called an **n-type semiconductor** (negatively charged electrons) and has a preponderance of electrons compared to holes.

The result is that at room temperature, there are a large number of carriers (electrons) in the conduction level, and the conductivity of the material increases significantly.

## **Majority and Minority Carriers:**

The electrons are called the **majority carriers** in n-type material. ( the n stands for the negative charge on an electron).

Although the majority of current carriers in *n*-type material are electrons, there are also a few holes that are created when electron-hole pairs are thermally generated

These holes are **not** produced by the addition of the pentavalent impurity atoms. Holes in an n-type material are called **minority carriers**.

#### P-Type Semiconductor

To increase the number of holes in intrinsic silicon, **trivalent** impurity atoms are added. These are atoms with three valence electrons such as boron (B), indium (In), and gallium (Ga).

A semiconductor that contains acceptor impurity atoms is called a **p-type semiconductor** (positively charged holes created) and has a preponderance of holes compared to electrons.

## Majority and Minority Carriers:

The holes are the **majority carriers** in **p**-type material. Although the majority of current carriers in **p**-type material are holes, there are also a few conduction-band electrons that are created when electron-hole pairs are thermally generated. These conduction-band electrons are **not** produced by the addition of the trivalent impurity atoms. Conduction-band electrons in **p**-type material are the minority carriers.

13

#### Electron and hole concentrations

A fundamental relationship between the electron and hole concentrations in a semiconductor in **thermal equilibrium** is given by :

$$n_o p_o = n_i^2$$

- $n_o$  is the thermal equilibrium concentration of free electrons.

- $p_o$  is the thermal equilibrium concentration of holes.

- $n_i$  is the intrinsic carrier concentration.

At room temperature ( $\mathbf{T} = 300 \text{ K}$ ), each donor atom donates a free electron to the semiconductor. If the donor concentration  $\mathbf{Nd}$  is much larger than the intrinsic concentration, we can approximate:

$$n_o \cong N_d$$

,  $N_d$  is donor concentration

the hole concentration is:

$$p_o = \frac{n_i^2}{N_d}$$

If the acceptor concentration Na is much larger than the intrinsic concentration, we can approximate:

$$p_o \cong N_a$$

,  $N_a$  is acceptor concentration

Then

$$n_o = \frac{n_i^2}{N_a}$$

<u>Thermal equilibrium:</u> the number of carriers in the conduction and valance band with no externally applied bias is called the equilibrium carrier concentration.

14

$(Thermal\ equilibrium = zero\ bias\ voltage)$

**EXAMPLE:** Calculate the thermal equilibrium electron and hole concentrations.

(a) Consider silicon at T = 300 K doped with phosphorus at a concentration of  $N_d = 10^{16}$  cm<sup>-3</sup>. Recall from Example 1.1 that  $n_i = 1.5 \times 10^{10}$  cm<sup>-3</sup>.

**Solution:** Since  $N_d \gg n_i$ , the electron concentration is

$$n_o \cong N_d = 10^{16} \, \text{cm}^{-3}$$

and the hole concentration is

$$p_o = \frac{n_i^2}{N_d} = \frac{(1.5 \times 10^{10})^2}{10^{16}} = 2.25 \times 10^4 \,\mathrm{cm}^{-3}$$

(b) Consider silicon at  $T = 300 \,\text{K}$  doped with boron at a concentration of  $N_a = 5 \times 10^{16} \,\text{cm}^{-3}$ .

**Solution:** Since  $N_a \gg n_i$ , the hole concentration is

$$p_o \cong N_a = 5 \times 10^{16} \, \text{cm}^{-3}$$

and the electron concentration is

$$n_o = \frac{n_i^2}{N_a} = \frac{(1.5 \times 10^{10})^2}{5 \times 10^{16}} = 4.5 \times 10^3 \,\mathrm{cm}^{-3}$$

#### **EXERCISE PROBLEM**

(a) Calculate the majority and minority carrier concentrations in silicon at

$T = 300 \text{ K for (i) } N_d = 2 \times 10^{16} \text{ cm}^{-3} \text{ and (ii) } N_a = 10^{15} \text{ cm}^{-3}.$  (b) Repeat part (a) for GaAs. (Ans. (a) (i)  $n_o = 2 \times 10^{16} \text{ cm}^{-3}$ ,  $p_o = 1.125 \times 10^4 \text{ cm}^{-3}$ ; (ii)  $p_o = 10^{15} \text{ cm}^{-3}$ ,  $n_o = 2.25 \times 10^5 \text{ cm}^{-3}$ ; (b) (i)  $n_o = 2 \times 10^{16} \text{ cm}^{-3}$ ,  $p_o = 1.62 \times 10^{-4} \text{ cm}^{-3}$ ; (ii)  $p_o = 10^{15} \text{ cm}^{-3}$ ,  $n_o = 3.24 \times 10^{-3} \text{ cm}^{-3}$ ).

15

$$Nc = ni \ exp \ rac{+|Ec-Efi|}{KT}$$

$Na = ni \ exp \ rac{+|Efp-Efi|}{KT}$   $Ni = Nc \ exp \ rac{-|Ec-Efi|}{KT}$   $Nv = Na \ exp \ rac{+|Ev-Efp|}{KT}$   $Nd = Ni \ exp \ rac{+|Efn-Efi|}{KT}$   $Na = Nv \ exp \ rac{-|Ev-Efp|}{KT}$   $Ni = Nd \ exp \ rac{-|Efn-Efi|}{KT}$   $Nv = Ni \ exp \ rac{+|Ev-Efi|}{KT}$   $Ni = Nv \ exp \ rac{-|Ev-Efi|}{KT}$

$Nc = Conduction \ band \ concentration.$

Ec = Energy of Conduction band.

Ni = Intrinsic Fermi level concentration.

*Efi = Energy of Internist Fermi level.*

$Nd = Donor\ electron\ concentration.$

Efn = Energy of Donor Fermi level.

Na = Acceptor hole concentration.

*Efp* = *Energy of Acceptor Fermi level.*

$Nv = Valance\ band\ concentration.$

Ev = Energy of Valance band.

K = Boltzmann's constant

T = Temperature of semiconductor.

The Fermi level is the energy at which the probability of occupation by an electron is exactly one-half  $\{0.5\}$  (lies midway between the two bands)

#### **Drift and Diffusion Currents**

- \* Two types of current exist in the semiconductors:

- 1. Drift Current Density

- 2. Diffusion Current Density

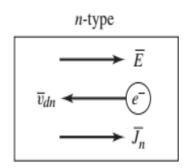

#### **Drift Current Density:**

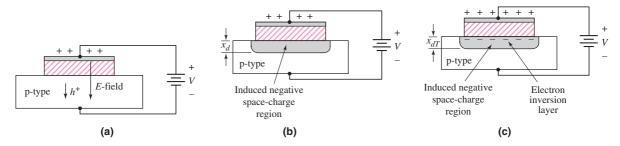

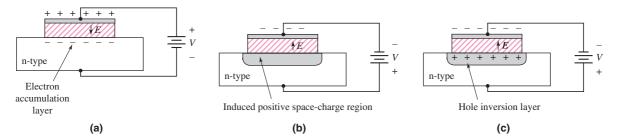

To understand drift, assume an electric field is applied to a semiconductor. An electric field E applied in one direction produces a force on the electrons in the *opposite* direction, because of the electrons' negative charge. The electrons acquire a **drift velocity**  $v_{dn}$  (in cm/s) which can be written as:

$$v_{dn} = -\mu_n E$$

drift velocity

$$\mu_n$$

: electron mobility in cm<sup>2</sup>/V-s — (constant)

The negative sign in Equation indicates that the electron drift velocity is opposite to that of the applied electric field.

The electron drift produces a **drift current density**  $J_n$  (A/cm<sup>2</sup>) given by:

$$J_n = -env_{dn} = -en(-\mu_n E) = +en\mu_n E$$

where  $\mathbf{n}$  is the electron concentration (#/cm3) and  $\mathbf{e}$ , is the magnitude of the electronic charge.

The conventional drift current (Jn) is in the opposite direction from the flow of negative charge  $(e^-)$ , which means that the drift current in an n-type semiconductor is in the same direction as the applied electric field (E).

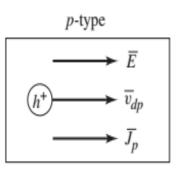

• Similarly (consider a p-type semiconductor)

An electric field E applied in one direction produces a force on the holes in the **same** direction, because of the positive charge on the holes.

17

$$v_{dp} = +\mu_p E$$

drift velocity

$\mu_p$ : **hole mobility** in cm<sup>2</sup>/V–s (constant)

The positive sign in Equation indicates that the hole drift velocity is in the same direction as the applied electric field.

The hole drift produces a **drift current density**  $J_p$  (A/cm<sup>2</sup>) given by:

$$J_p = +epv_{dp} = +ep(+\mu_p E) = +ep\mu_p E$$

where  $\mathbf{p}$  is the hole concentration (#/cm3) and  $\mathbf{e}$  is again the magnitude of the electronic charge.

The conventional drift current (Jp) is in the same direction as the flow of positive charge  $(h^+)$ , which means that the drift current in a p-type material is also in the same direction as the applied electric field (E)

<u>Since a semiconductor</u> contains both electrons and holes, the total drift current density is the sum of the electron and hole components. The total drift current density is then written as:

$$J = en\mu_n E + ep\mu_p E = \sigma E = \frac{1}{\rho} E$$

Where

$$\sigma = en\mu_n + ep\mu_p$$

$\sigma$  is the **conductivity** of the semiconductor in  $(\Omega$ –cm)<sup>-1</sup>

$\rho$  is the **resistivity** of the semiconductor in ( $\Omega$ –cm)

#### **EXERCISE PROBLEM**

Consider n-type GaAs at T = 300 K doped to a concentration of  $N_d = 2 \times 10^{16}$  cm<sup>-3</sup>. Assume mobility values of  $\mu_n = 6800$  cm<sup>2</sup>/V-s and  $\mu_p = 300$  cm<sup>2</sup>/V-s. (a) Determine the resistivity of the material. (b) Determine the applied electric field that will induce a drift current density of 175 A/cm<sup>2</sup>. (Ans. (a)  $0.0460 \Omega$ -cm, (b) 8.04 V/cm).

18

#### **EXAMPLE**

Objective: Calculate the drift current density for a given semiconductor.

Consider silicon at  $T=300\,\mathrm{K}$  doped with arsenic atoms at a concentration of  $N_d=8\times10^{15}\,\mathrm{cm}^{-3}$ . Assume mobility values of  $\mu_n=1350\,\mathrm{cm}^2/\mathrm{V}$ –s and  $\mu_p=480\,\mathrm{cm}^2/\mathrm{V}$ –s. Assume the applied electric field is  $100\,\mathrm{V/cm}$ .

**Solution:** The electron and hole concentrations are

$$n \cong N_d = 8 \times 10^{15} \,\mathrm{cm}^{-3}$$

and

$$p = \frac{n_i^2}{N_d} = \frac{(1.5 \times 10^{10})^2}{8 \times 10^{15}} = 2.81 \times 10^4 \,\mathrm{cm}^{-3}$$

Because of the difference in magnitudes between the two concentrations, the conductivity is given by

$$\sigma = e\mu_n n + e\mu_p p \cong e\mu_n n$$

or

$$\sigma = (1.6 \times 10^{-19})(1350)(8 \times 10^{15}) = 1.73(\Omega - \text{cm})^{-1}$$

The drift current density is then

$$J = \sigma E = (1.73)(100) = 173 \text{ A/cm}^2$$

**Comment:** Since  $n \gg p$ , the conductivity is essentially a function of the electron concentration and mobility only. We may note that a current density of a few hundred amperes per square centimeter can be generated in a semiconductor.

19

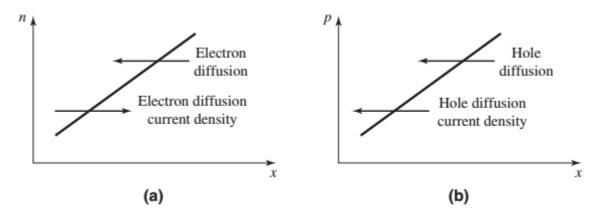

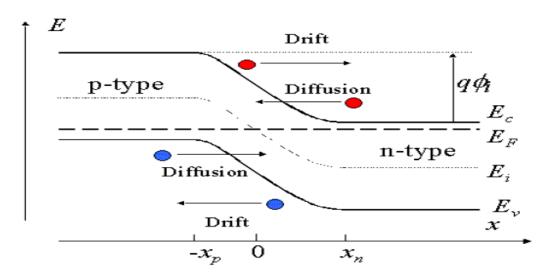

#### **Diffusion Current Density:**

In the diffusion process, particles flow from a region of high concentration to a region of lower concentration.

For example, consider an electron concentration that varies as a function of distance  $\mathbf{x}$ , as shown in Figure (a) .The diffusion of electrons from a high-concentration region to a low-concentration region produces a flow of electrons in the negative  $\mathbf{x}$  direction. Since electrons are negatively charged, the conventional current direction is in the positive  $\mathbf{x}$  direction.

• The diffusion current density due to the diffusion of electrons can be written as (for one dimension)

$$J_n = eD_n \frac{dn}{dx}$$

dn/dx is the gradient of the electron concentration

In Figure (b), the hole concentration is a function of distance. The diffusion of holes from a high-concentration region to a low-concentration region produces a flow of holes in the negative  $\mathbf{x}$  direction. (Conventional current is in the direction of the flow of positive charge.)

• The diffusion current density due to the diffusion of holes can be written as (for one dimension)

$$J_p = -eD_p \frac{dp}{dx}$$

dp/dx is the gradient of the hole concentration

Dn is the electron diffusion coefficient.

Dp is the hole diffusion coefficient.

#### **EXAMPLE**

Objective: Calculate the diffusion current density for a given semiconductor.

Consider silicon at T=300 K. Assume the electron concentration varies linearly from  $n=10^{12}$  cm<sup>-3</sup> to  $n=10^{16}$  cm<sup>-3</sup> over the distance from x=0 to  $x=3~\mu$ m. Assume  $D_n=35$  cm<sup>2</sup>/s.

Solution: We have

$$J_n = eD_n \frac{dn}{dx} = eD_n \frac{\Delta n}{\Delta x} = (1.6 \times 10^{-19})(35) \left( \frac{10^{12} - 10^{16}}{0 - 3 \times 10^{-4}} \right)$$

Or

$$J_n = 187 \text{ A/cm}^2$$

**Comment:** Diffusion current densities on the order of a few hundred amperes per square centimeter can also be generated in a semiconductor.

#### **EXERCISE PROBLEM**

Consider silicon at T=300 K. Assume the hole concentration is given by  $p=10^{16}e^{-x/L_p}$  (cm<sup>-3</sup>), where  $L_p=10^{-3}$  cm. Calculate the hole diffusion current density at (a) x=0 and (b)  $x=10^{-3}$  cm. Assume  $D_p=10$  cm<sup>2</sup>/s. (Ans. (a) 16 A/cm<sup>2</sup>, (b) 5.89 A/cm<sup>2</sup>)

The mobility values in the drift current equations and the diffusion coefficient values in the diffusion current equations are not independent quantities. They are related by the **Einstein relation**, which is:

$$\frac{D_n}{\mu_n} = \frac{D_p}{\mu_p} = \frac{kT}{e} \cong 0.026 \text{ V}$$

At room temperature.

The **total** current density is the sum of the drift and diffusion components. Fortunately, in most cases only one component dominates the current at any one time in a given region of a semiconductor.

21

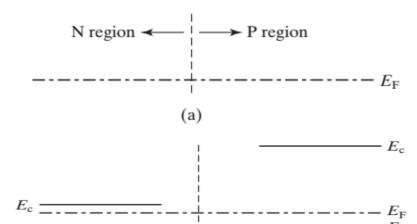

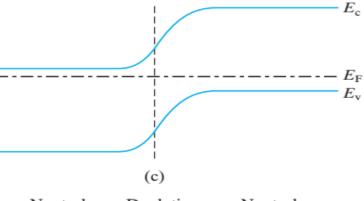

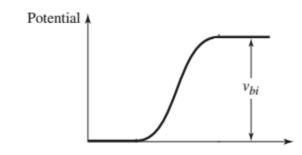

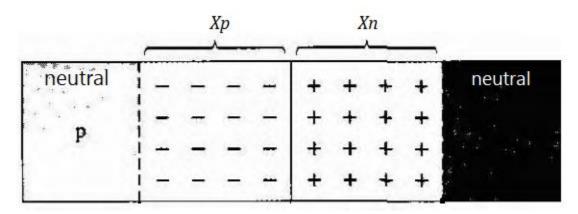

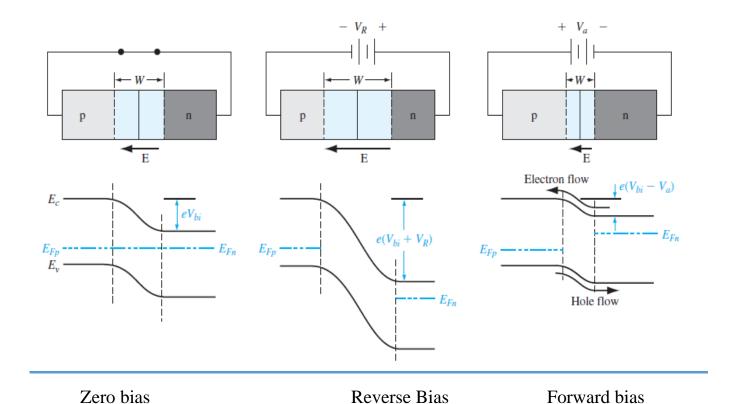

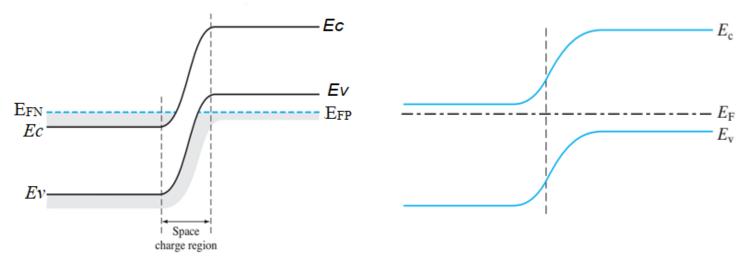

#### THE Equilibrium pn JUNCTION

P and N layers are uniformly doped at acceptor density Na, and donor density Nd, respectively. This idealized PN junction is known as a *step junction*.

$$n \approx 0$$

and  $p \approx 0$  in the depletion layer

The term **depletion layer** means that the layer is depleted of electrons and holes.

(No mobile electrons or holes).

Why the n-type material are lower than the p-type material?

#### Because:

The trivalent impurities exert lower forces on the outer-shell electrons than the pentavalent impurities.

#### That is mean:

The lower forces in **p**-type materials means that the electron orbits have greater energy than the electron orbits in the **n**-type materials.

**Depletion region = Space charge region**

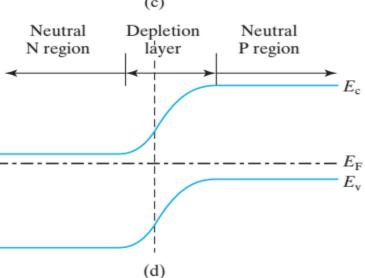

Energy - band diagram of a pn junction in thermal equilibrium

$Vbi = built - in - potential\ barrier\ \underline{Or}\ built-in\ voltage\ (volts)$

$\Phi Fn = static potential for n type (volts).$

$\Phi Fp = static potential for p type (volts).$

$$Nd = Ni exp \frac{+|Efn-Efi|}{KT}$$

,  $e \Phi Fn = Efi - Efn$

$$Nd = Ni \ exp \ \frac{-(e \Phi Fn)}{KT}$$

,  $\Phi Fn = \frac{Efi - Efn}{e}$

$$\frac{Nd}{Ni} = exp \frac{-(e \phi Fn)}{KT}$$

taking the lin of both sides

$$\ln \frac{Nd}{Ni} = \frac{-(e \Phi F n)}{KT}$$

$$\therefore \Phi F n = -\frac{KT}{e} \ln \frac{Nd}{Ni}$$

Similarity, in the P – region

$$Na = ni \ exp \ rac{+|Efi-Efp|}{KT}$$

,  $e \Phi Fp = Efi - Efp$

$$\therefore \Phi F p = + \frac{KT}{e} \ln \frac{Na}{Ni} \qquad , \qquad \Phi F p = \frac{Efi - Efp}{e}$$

Finally, the built – in potential barrier for the pn junction is formed by :

$$Vbi = \frac{KT}{e} \ln \frac{NaNd}{Ni^2}$$

where  $\frac{KT}{e}$  = vt (thermal voltage) vt = (25 – 26 mV)

## **EXAMPLE**

Objective: Calculate the built-in potential barrier of a pn junction.

Consider a silicon pn junction at T = 300 K, doped at  $N_a = 10^{16}$  cm<sup>-3</sup> in the p-region and  $N_d = 10^{17}$ cm<sup>-3</sup> in the n-region.

**Solution:** From the results of Example 1.1, we have  $n_i = 1.5 \times 10^{10} \text{cm}^{-3}$  for silicon at room temperature. We then find

24

$$V_{bi} = V_T \ln \left( \frac{N_a N_d}{n_i^2} \right) = (0.026) \ln \left[ \frac{(10^{16})(10^{17})}{(1.5 \times 10^{10})^2} \right] = 0.757 \text{ V}$$

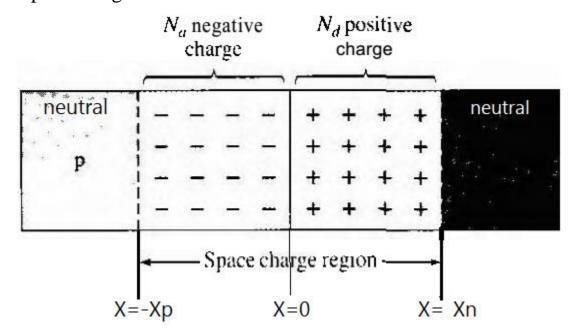

#### **Electric Field of pn JUNCTION**

An electric field is created in the depletion region by the separation of positive and negative space charge densities.

The electric field is determined from Poisson's equation which, for a one dimensional analysis, is

$$\frac{d^2 \Phi(x)}{dx^2} = \frac{-\rho(x)}{\varepsilon_s} = -\frac{dE(x)}{dx}$$

Where  $\phi(x)$  is the electric potential {phi},  $\mathbf{E}(\mathbf{x})$  is the electric field,  $\rho(x)$  is the volume charge density {Rho} and  $\varepsilon_s$  is the permittivity of the semiconductor {Epsilon}

25

$$\varepsilon_s = \varepsilon_r * \varepsilon_o$$

$\varepsilon_r = \text{Relative permittivity or dielectric constant} = 11.7$

$$\varepsilon_o = \text{Permittivity of free space} = 8.85* 10^{-14} \text{ (farad/cm)}$$

∴

$$\varepsilon_s$$

= (11.7) (8.85\* 10<sup>-14</sup>) = 103.5 (F/cm)

$$\rho(x) = -eNa$$

,  $-Xp \le X \le 0$

$$\rho(x) = eNd \qquad , \qquad 0 \le X \le Xn$$

The electric field in the p - region is found by integrating Equation:

$$-dE(x) = -\frac{\rho(x)}{\varepsilon_S}dx$$

$$\int dE(x) = \int \frac{\rho(x)}{\varepsilon_s} dx$$

$$E(x) = \int \frac{\rho(x)}{\varepsilon_s} dx = -\int \frac{eNa}{\varepsilon_s} dx$$

$$\therefore E(x) = \frac{-eNa}{\varepsilon_s} x + C_1$$

where  $C_1$  is a constant of integration

At

$$x = -xp \longrightarrow E(x) = 0$$

$$\therefore 0 = \frac{-eNa}{\varepsilon_s} - xp + C1$$

$$\therefore C_1 = \frac{-eNa}{\varepsilon_s} xp$$

$$\therefore E = \frac{-eNa}{\varepsilon_S} x - \frac{eNa}{\varepsilon_S} xp$$

The electric field is assumed to be zero in the neutral p region for X < -Xp since the currents are zero in thermal equilibrium.

$$\therefore E(x) = \frac{-eNa}{\varepsilon_s} (x + xp) \qquad \text{at } -Xp \le X \le 0$$

at

$$-Xp \le X \le 0$$

In the n region, the electric field is

$$E(x) = \int \frac{eNd}{\varepsilon_s} dx$$

$$E(x) = \frac{eNd}{\varepsilon_s} x + C_2$$

where C<sub>2</sub> is a constant of integration

At

$$x = xn$$

$\longrightarrow$   $E(x) = 0$

$$\therefore 0 = \frac{eNd}{\varepsilon_s} xn + C2$$

$$\therefore C_2 = \frac{-eNd}{\varepsilon_s} xn$$

The electric field is assumed to be zero in the neutral n region for X > Xn since the currents are zero in thermal equilibrium.

$$\therefore E(x) = \frac{-eNd}{\varepsilon_S} (xn - x)$$

at

$$0 \le X \le Xn$$

or

$$\therefore E(x) = \frac{eNd}{\varepsilon_s} (x - xn)$$

at

$$0 \le X \le Xn$$

$\therefore$  Max value of E(x) at x = 0

$$|Emax p| = |Emax n|$$

$$\frac{-eNa}{\varepsilon_s} xp = \frac{-eNd}{\varepsilon_s} xn$$

$$NaXp = NdXn$$

- ❖ That is mean the number of negative charges per unit area in the p-region is equal to the number of positive charges per unit area in the n-region.

- ❖ An electric field exists in the depletion region even when no voltage is applied between the p-and n- regions.

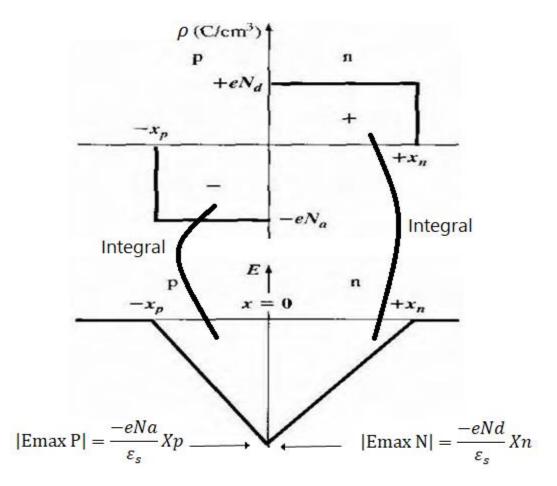

## Now another way to determine vbi

The potential in the junction is found by integrating the electric field.

in the p-region.

$$\frac{d^2\Phi}{dx^2} = -\frac{dE(x)}{dx} , \quad E(x) = -\frac{d\Phi(x)}{dx}$$

$$\int d\Phi(x) = -\int E(x)dx$$

$$\phi(x) = -\int \frac{-eNa}{\varepsilon_s} (x + xp) \, dx$$

$$\phi(x) = \frac{eNa}{\varepsilon_s} \left( \frac{x^2}{2} + xp . x \right) + \bar{C}_I \quad \text{where } \overline{C}_I \text{ is a constant of integration}$$

The potential is assumed to be zero at X = -Xp.  $\phi(x) = 0$

$$\therefore 0 = \frac{-eNa}{\varepsilon_S} \left( \frac{xp^2}{2} \right) + \overline{C}_I \qquad \longrightarrow \quad \overline{C}_I = \frac{eNa}{2\varepsilon_S} xp^2 \text{ or } \overline{C}_I = \frac{eNa}{\varepsilon_S} \frac{xp^2}{2}$$

$$\therefore \varphi(x) = \frac{eNa}{\varepsilon_S} \left( \frac{x^2}{2} + xp . x \right) + \frac{eNa}{\varepsilon_S} \frac{xp^2}{2}$$

$$\phi(x) = \frac{eNa}{\varepsilon_s} \left\{ \left( \frac{x^2}{2} + xp . x \right) + \frac{xp^2}{2} \right\} \longrightarrow *2$$

$$2\phi(x) = \frac{eNa}{\varepsilon_s} \{ (x^2 + 2xp . x) + xp^2 \}$$

$$2\phi(x) = \frac{eNa}{\varepsilon_s} (x + xp)^2 \longrightarrow /2$$

$$\phi(x) = \frac{eNa}{2\varepsilon_s} (x + xp)^2 \qquad -Xp \le X \le 0$$

In the n region, the potential is

$$\phi(x) = \int \frac{eNd}{\varepsilon_S} (xn - x) dx$$

$$\phi(x) = \frac{eNd}{\varepsilon_s} (xn \cdot x - \frac{x^2}{2}) + \bar{C}_2 \quad \text{where } \overline{C}_2 \text{ is a constant of integration}$$

$$\overline{C}_2 = \frac{eNa}{2\varepsilon_s} xp^2$$

In the n-region. The potential is not to be zero at X = Xn

$$\phi(x) = \frac{eNd}{\varepsilon_S} (xn \cdot x - \frac{x^2}{2}) + \frac{eNa}{2\varepsilon_S} xp^2 \qquad 0 \le X \le Xn$$

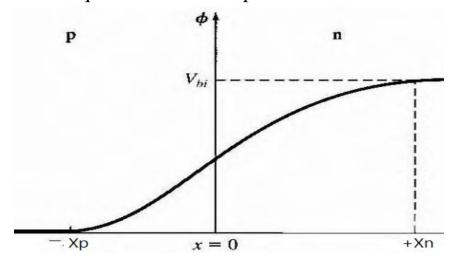

Figure below is a plot of the potential through the junction. The magnitude of the potential at X = Xn is equal to the built-in potential barrier.

Electric potential through the space charge\_of a uniformly doped pn junction.

$$\therefore Vbi = |\phi(X = Xn)| = \frac{e}{2\varepsilon_s} (NdX^2n + NaX^2p) \quad ----a$$

### Space charge width

NaXp = NdXn

We can determine the distance that the space charge region extends into the p and n regions from the junction. This distance is known as the space charge width

$$Xp = \frac{NdXn}{Na} - - - b$$

substituting equation  $b$  into equation  $a$  and solving for  $Xn$

$$Vbi = \frac{e}{2\varepsilon_a} (NdX^2n + Na\frac{Nd^2Xn^2}{Na^2})$$

$$Vbi = \frac{e}{2\varepsilon_c} (NdX^2 n + \frac{Nd^2Xn^2}{Na})$$

$$Vbi = \frac{e}{2\varepsilon_S} \{ X^2 n (Nd + \frac{Nd^2}{Na}) \} \qquad , \qquad X^2 n \left( Nd + \frac{Nd^2}{Na} \right) = \frac{2vbi\varepsilon_S}{e}$$

$$\therefore X^2 n = \frac{2vbi\varepsilon_s}{e} * \frac{1}{Nd + \frac{Nd^2}{Na}} \qquad , \qquad \therefore X^2 n = \frac{2vbi\varepsilon_s}{e} * \frac{Na}{NaNd + Nd^2}$$

$$\therefore Xn = \sqrt{\frac{2vbi\varepsilon_s}{e} * \frac{Na}{Nd} \left[ \frac{1}{Na + Nd} \right]}$$

The width of the depletion region, Xn extending into the n-type region for the case of zero applied voltage.

Similarly, if we solve for Xp

$$\therefore Xp = \sqrt{\frac{2vbi\varepsilon_s}{e} * \frac{Nd}{Na} \left[ \frac{1}{Na + Nd} \right]}$$

The width of the depletion region, Xp extending into the p-type region for the case of zero applied voltage.

The total depletion or space charge width W is the sum of the two components, or

$$W = Xn + Xp$$

$$\therefore W = \sqrt{\frac{2vbi\varepsilon_s}{e} * \left[\frac{Na + Nd}{NaNd}\right]}$$

$\therefore$  Wmax is achieved when Na = Nd

#### **EXAMPLE**

Calculate the space charge width (W) and electric field (E) in a pn junction. Consider a silicon at  $T = 300^{0}$  K with doping of  $Na = 10^{16}$  cm<sup>-3</sup> and  $Nd = 10^{15}$  cm<sup>-3</sup> and  $Xn = 0.864 \ \mu m$ .

30

Solution:

$$Vbi = \frac{KT}{e} \ln \frac{NaNd}{Ni^2}$$

$$Vbi = (0.0259) \ln \frac{(10^{16})(10^{15})}{(1.5*10^{10})^2}$$

$$\therefore Vbi = 0.635 \ volt$$

$$W = \left\{ \frac{2\epsilon_s V_{bi}}{e} \left[ \frac{N_a + N_d}{N_a N_d} \right] \right\}^{1/2}$$

$$= \left\{ \frac{2(11.7)(8.85 \times 10^{-14})(0.635)}{1.6 \times 10^{-19}} \left[ \frac{10^{16} + 10^{15}}{(10^{16})(10^{15})} \right] \right\}^{1/2}$$

$$= 0.951 \times 10^{-4} \text{ cm} = 0.951 \ \mu\text{m}$$

$$E_{\text{max}} = \frac{-eN_d x_n}{\epsilon_s} = \frac{-(1.6 \times 10^{-19})(10^{15})(0.864 \times 10^{-4})}{(11.7)(8.85 \times 10^{-14})}$$

$$= 1.34 \times 10^4 \text{ V/cm}$$

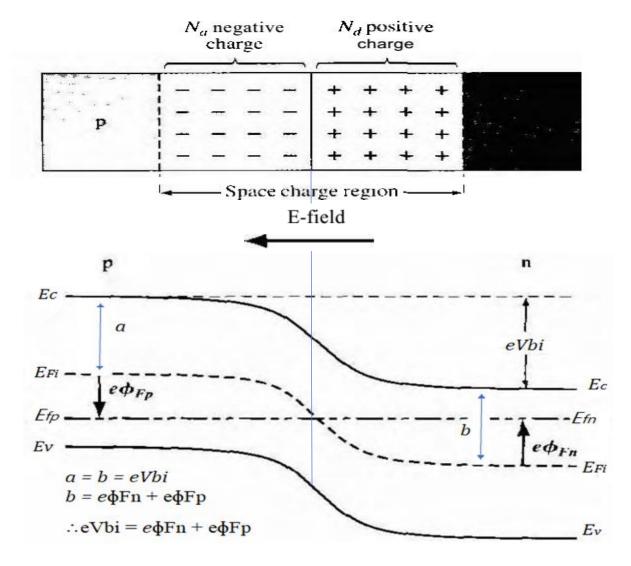

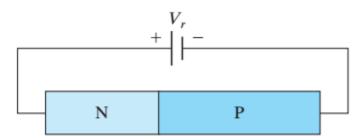

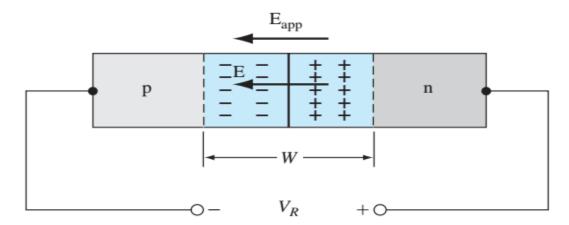

#### **Reverse -Biased pn Junction**

When a positive voltage is applied to the N region and negative voltage is applied to the P region, the PN junction is said to be **reverse-biased**.

The applied voltage VR induces an applied electric field,  $E_A$ , in the semiconductor. The direction of this applied field is the same as that of the E-field in the space-charge region. The magnitude of the electric field in the space charge region must increase above the thermal-equilibrium value due to the applied voltage.

31

There is no current across the pn junction.

The electric field  $(\mathbf{E}_A)$  originates positive and negative charges; this means that the number of positive and negative charges must increase if the electric field increases, Then the space charge width  $(\mathbf{W})$  increases.

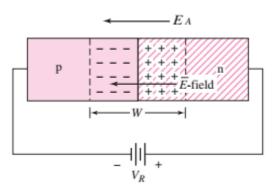

In the reverse biased the Fermi energy level will not be constant through the system. Figure below shows the energy-band diagram of the pn junction

The total potential barrier, indicated by  $V_{total}$  has increased. This applied potential is the reverse – bias condition.

$$V_{\text{total}} = |\Phi F n| + |\Phi F p| + V_{R}$$

$$V_{total} = V_{bi} + V_R$$

The total space charge width can he written as:

$$\therefore W = \sqrt{\frac{2\varepsilon_s(vbi + VR)}{e} * \left[\frac{Na + Nd}{NaNd}\right]}$$

32

$$Vbias = VR$$

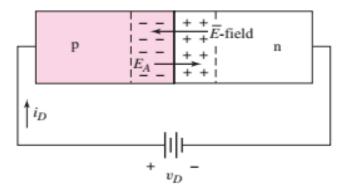

#### Forward -Biased pn Junction

When a positive voltage is applied to the P region and negative voltage is applied to the N region, the PN junction is said to be **forward-biased**.

If a positive voltage  $V_D$  is applied to the p-region, the potential barrier decreases. The applied electric field, EA, induced by the applied voltage is in the opposite direction from that of the thermal equilibrium space-charge E-field.

There are current across the pn junction.

The total potential barrier, indicated by  $V_{total}$  has decreased. This applied potential is the forward – bias condition.

$$V_{\text{total}} = |\Phi F n| + |\Phi F p| - V_D$$

$$V_{total} = V_{bi} - V_{D}$$

The total space charge width can he written as:

$$W = \sqrt{\frac{2\varepsilon_s(vbi\_VD)}{e} * \left[\frac{Na + Nd}{NaNd}\right]}$$

$$Vbias = V_D$$

$$Vtotal = Vbi - V_D$$

#### **EXAMPLE**

Calculate the width of the space charge region in a pn junction when a reversebiased voltage is applied.

Again consider a silicon pn junction at T = 300 K with doping concentrations of  $N_a = 10^{16}$  cm<sup>-3</sup> and  $N_d = 10^{15}$  cm<sup>-3</sup>. Assume that  $n_i = 1.5 \times 10^{10}$  cm<sup>-3</sup> and  $V_R = 5$  V.

#### **Solution:**

$$Vbi = (0.0259) \ln \frac{(10^{16})(10^{15})}{(1.5*10^{10})^2}$$

::  $Vbi = 0.635 \text{ volt}$

$$W = \left\{ \frac{2(11.7)(8.85 \times 10^{-14})(0.635 + 5)}{1.6 \times 10^{-19}} \left[ \frac{10^{16} + 10^{15}}{(10^{16})(10^{15})} \right] \right\}^{1/2}$$

$$W = 2.83 \times 10^{-4} \,\mathrm{cm} = 2.83 \,\mu\mathrm{m}$$

#### **Electric Field For Reverse -Biased pn Junction**

The magnitude of the electric field in the depletion region increases with an applied reverse-biased voltage.

Since *Xn* and *Xp* increase with reverse-biased voltage, the magnitude of the electric field also increases.

The maximum electric field still occurs at X = 0.

The electric field is given by Equations:

$$E_{\text{max}} = \frac{-eN_d x_n}{\epsilon_s} = \frac{-eN_a x_p}{\epsilon_s}$$

Substitutive on *Xn*

$$Emax = \frac{-eNd}{\varepsilon_{S}} * \sqrt{\frac{2\varepsilon_{S}(vbi+VR)}{e} * \frac{Na}{Nd} \left[\frac{1}{Na+Nd}\right]}$$

Square both sides

$$Emax^{2} = \frac{e^{2}Nd^{2}}{\varepsilon_{s}^{2}} \frac{2\varepsilon_{s}(vbi+VR)}{e} * \frac{Na}{Nd} \left[ \frac{1}{Na+Nd} \right]$$

$$E_{\text{max}} = -\left\{\frac{2e(V_{bi} + V_R)}{\epsilon_s} \left(\frac{N_a N_d}{N_a + N_d}\right)\right\}^{1/2}$$

We can show that the maximum electric field in the pn junction can also be written as

$$E_{\text{max}} = \frac{-2(V_{bi} + V_{R})}{W}$$

35

Dr F.H & Firas

n

$+x_n$

#### **EXAMPLE**

A silicon pn junction at  $T = 300^{\circ}$  K with  $Nd = 5*10^{15}$ cm<sup>-3</sup> and  $Na = 5*10^{16}$ cm<sup>-3</sup>. Assume  $ni = 1.5*10^{10}$ cm<sup>-3</sup>. Calculate the reverse-voltage that will produce a maximum electric field of  $|Emax| = 1.25*10^{5}$  V/cm.

#### **Solution:**

$$E_{\text{max}} = -\left\{\frac{2e(V_{bi} + V_R)}{\epsilon_s} \left(\frac{N_a N_d}{N_a + N_d}\right)\right\}^{1/2}$$

$$Vbi + V_R = \frac{\varepsilon_S Emax^2}{2e} \left( \frac{Na + Nd}{NaNd} \right)$$

$$= \frac{(11.7)(8.85 \times 10^{-14})(1.25 \times 10^5)^2}{2(1.6 \times 10^{-19})} \left[ \frac{5 \times 10^{16} + 5 \times 10^{15}}{(5 \times 10^{16})(5 \times 10^{15})} \right] = 11.1 \text{ V}$$

The built – in potential barrier,  $\overline{Vbi} = \frac{KT}{e} \ln \frac{NaNd}{Ni^2}$

$$Vbi = (0.0259) \ln \frac{(5*10^{16})(5*10^{15})}{(1.5*10^{10})^2}$$

$$Vbi = 0.718 \text{ V}$$

$$V_R = 11.1 - 0.718 = 10.4 \text{ V}$$

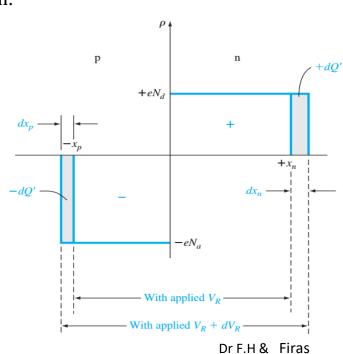

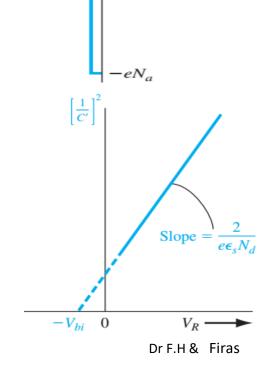

#### Junction Capacitance For Reverse -Biased pn Junction

Since we have a separation of positive and negative charges in the depletion region, a capacitance is associated with the pn junction.

An increase in the reverse-biased voltage *dVR* will uncover additional positive charges in the n region and additional negative charges in the p region. The junction capacitance is defined as:

$$C' = \frac{dQ'}{dV_R}$$

$$dQ' = eN_d dx_n = eN_a dx_p$$

The differential charge dQ\_is in units of Coul/cm<sup>2</sup> so that the capacitance C is in the units (F/cm<sup>2</sup>)

$$C' = \frac{dQ'}{dV_R} = eN_d \frac{dx_n}{dV_R}$$

$$x_n = \left\{ \frac{2\epsilon_s(V_{bi} + V_R)}{e} \left[ \frac{N_a}{N_d} \right] \left[ \frac{1}{N_a + N_d} \right] \right\}^{1/2}$$

$$C' = \left\{ \frac{e\epsilon_s N_a N_d}{2(V_{bi} + V_R)(N_a + N_d)} \right\}^{1/2}$$

#### **EXAMPLE**

To calculate the junction capacitance of a pn junction. Consider

Again consider a silicon pn junction at T = 300 K with doping concentrations of  $N_a = 10^{16}$  cm<sup>-3</sup> and  $N_d = 10^{15}$  cm<sup>-3</sup>. Assume that  $n_i = 1.5 \times 10^{10}$  cm<sup>-3</sup> and  $V_R = 5$  V.

#### **Solution**

$$C' = \left\{ \frac{(1.6 \times 10^{-19})(11.7)(8.85 \times 10^{-14})(10^{16})(10^{15})}{2(0.635 + 5)(10^{16} + 10^{15})} \right\}^{1/2}$$

$$C' = 3.66 \times 10^{-9} \,\text{F/cm}^2$$

If the cross-sectional area of the pn junction is, for example,  $A = 10^{-4}$  cm<sup>2</sup>, then the total junction capacitance is

$$C = C' \cdot A = 0.366 \times 10^{-12} \,\text{F} = 0.366 \,\text{pF}$$

Another expression for the junction capacitance that is:

$$C' = \frac{\epsilon_s}{W}$$

#### EXERCISE PROBLEM

Consider a GaAs pn junction at T = 300 K doped to  $N_a = 5 \times 10^{15}$  cm<sup>-3</sup> and  $N_d = 2 \times 10^{16}$  cm<sup>-3</sup>. (a) Calculate  $V_{bi}$ . (b) Determine the junction capacitance C' for  $V_R = 4V$

#### **One-Sided Junctions (Na >> Nd)**

Consider a special pn junction called the one-sided junction. for example, Na >> Nd this junction is referred to as a  $p^+$  n junction. (Xn >> Xp)

$$x_n = \left\{ \frac{2\epsilon_s(V_{bi} + V_R)}{e} \left[ \frac{N_a}{N_d} \right] \left[ \frac{1}{N_a + N_d} \right] \right\}^{1/2}$$

يهمل لان قيمته صغيرة جدا

$$\therefore Xn = \left\{\frac{2\varepsilon s(Vbi + VR)}{eNd}\right\}^{1/2}$$

$$Xp = \left\{ \frac{2\varepsilon s(Vbi+VR)Nd}{eNa^2} \right\}^{1/2} \cong 0$$

لان Na كمية كبيرة و هي في المقام و تربيع ايضا

:. The total space charge width is:

$$W \approx \left\{ \frac{2\epsilon_s(V_{bi} + V_R)}{eN_d} \right\}^{1/2}$$

(One-Sided)  $Xn >> Xp$   $W \approx Xn$

The junction capacitance of the p<sup>+</sup> n junction reduces to

$$C' \approx \left\{ \frac{e\epsilon_s N_d}{2(V_{bi} + V_R)} \right\}^{1/2} \qquad C' = \frac{\epsilon_s}{W}$$

The depletion layer capacitance of a one-sided junction is a function of the doping concentration in the low-doped region (Nd).

The equation of capacitance can be weitten as:

$$\left(\frac{1}{C'}\right)^2 = \frac{2(V_{bi} + V_R)}{e\epsilon_s N_d}$$

which shows that the inverse capacitance squared is a linear function of applied reverse-biased voltage.

$+x_n$

#### **EXAMPLE**

Determine the impurity doping (Na and Nd) in a p<sup>+</sup> n Si-junction for parameters T = 300  $^{0}$  K ,  $ni = 1.5 * 10^{10}$  cm<sup>-3</sup> , Vbi = 0.72V and slope =  $6.15*10^{15}$ (F/cm<sup>2</sup>)<sup>-2</sup>.V<sup>-1</sup>

#### **Solution**:

$$N_d = \frac{2}{e \, \epsilon_s} \cdot \frac{1}{slope} = \frac{2}{(1.6 \times 10^{-19})(11.7)(8.85 \times 10^{-14})(6.15 \times 10^{15})}$$

$$N_d = 1.96 \times 10^{15} \,\mathrm{cm}^{-3}$$

$$V_{bi} = V_t \ln \left( \frac{N_a N_d}{n_i^2} \right)$$

$$N_a = \frac{n_i^2}{N_d} \exp\left(\frac{V_{bi}}{V_t}\right) = \frac{(1.5 \times 10^{10})^2}{1.963 \times 10^{15}} \exp\left(\frac{0.725}{0.0259}\right)$$

$$N_a = 1.64 \times 10^{17} \,\mathrm{cm}^{-3}$$

#### Comment

The results of this example show that  $N_a \gg N_d$ ; therefore the assumption of a one-sided junction was valid.

#### **EXERCISE PROBLEM**

The experimentally measured junction capacitance of a one-sided silicon n<sup>+</sup>p junction biased at  $V_R = 3$  V and at T = 300 K is C = 0.105 pF. The built-in potential barrier is found to be  $V_{bi} = 0.765$  V. The cross-sectional area is  $A = 10^{-5}$  cm<sup>2</sup>. Find the doping concentrations.

#### Ideal Current-Voltage Relationship

$$I = I_s \left[ \exp\left(\frac{eV_a}{nkT}\right) - 1 \right] \qquad I = I_s \left[ \exp\left(\frac{V_a}{nVt}\right) - 1 \right]$$

The parameter *IS* is the *reverse-bias saturation current*. For silicon pn junctions, typical values of *IS* are in the range of  $10^{-18}$  to  $10^{-20}$  A.

The actual value depends on the doping concentrations and is also proportional to the cross-sectional area of the junction.

VT = 0.026 V at room temperature.

The parameter **n** is usually called the emission coefficient or ideality factor, and its value is in the range  $1 \le \mathbf{n} \le 2$ .

The emission coefficient  $\mathbf{n}$  takes into account any recombination of electrons and holes in the space-charge region.

#### **EXAMPLE**

Objective: Determine the current in a pn junction diode.

Consider a pn junction at T = 300 K in which  $I_S = 10^{-14}$  A and n = 1. Find the diode current for  $v_D = +0.70$  V and  $v_D = -0.70$  V.

**Solution:** For  $v_D = +0.70$  V, the pn junction is forward-biased and we find

$$i_D = I_S \left[ e^{\left(\frac{v_D}{V_T}\right)} - 1 \right] = (10^{-14}) \left[ e^{\left(\frac{+0.70}{0.026}\right)} - 1 \right] \Rightarrow 4.93 \text{ mA}$$

For  $v_D = -0.70 \,\mathrm{V}$ , the pn junction is reverse-biased and we find

$$i_D = I_S \left[ e^{\left(\frac{v_D}{V_T}\right)} - 1 \right] = (10^{-14}) \left[ e^{\left(\frac{-0.70}{0.026}\right)} - 1 \right] \cong -10^{-14} \,\text{A}$$

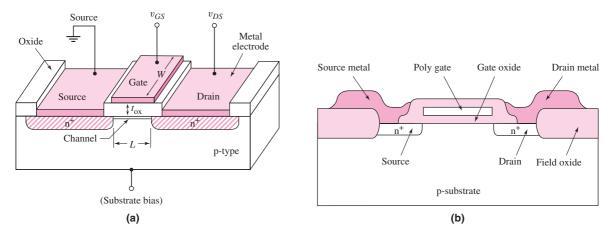

### **Semiconductor devices**

#### 1. Microwaves devices

That works at frequencies band of microwaves (1Ghz to 3000Ghz) (300 to 0.01 cm)

- a. Tunnel diode.

- b. Back -word diode.

- c. IMPATT diode (Impact ionization Avalanche Transition Time).

- d. Baritt Diode.

- e. Gunn Diode.

#### 2. Photonic devices

Photonic devices are devices in which the basic particle of light—the photon—plays a major role

b. Light source devices

LAESR (Light Amplification by stimulated Emission Radiation)

| Designation   | Frequency range (GHz) | Wavelength (cm) |

|---------------|-----------------------|-----------------|

| VHF           | 0.1-0.3               | 300.00-100.00   |

| UHF           | 0.3-1.0               | 100.00-30.00    |

| L band        | 1.0-2.0               | 30.00-15.00     |

| S band        | 2.0-4.0               | 15.00-7.50      |

| C band        | 4.0-8.0               | 7.50-3.75       |

| X band        | 8.0-13.0              | 3.75-2.31       |

| Ku band       | 13.0-18.0             | 2.31-1.67       |

| K band        | 18.0-28.0             | 1.67-1.07       |

| Ka band       | 28.0-40.0             | 1.07-0.75       |

| Millimeter    | 30.0-300.0            | 1.00-0.10       |

| Submillimeter | 300.0-3000.0          | 0.10-0.01       |

41

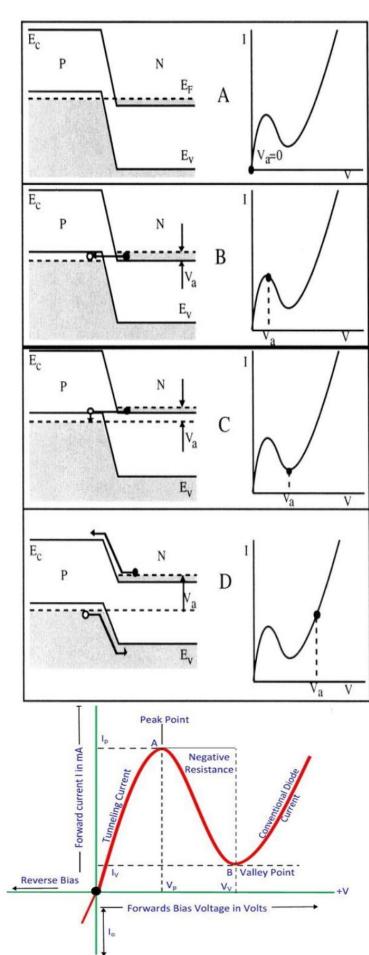

#### **Tunnel diode**

#### <u>Definition of tunnel diode:</u>

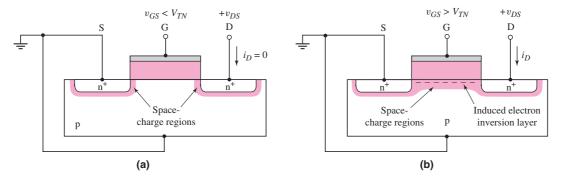

- A Tunnel diode is a heavily doped p-n junction diode in which the electric current decreases as the voltage increases and have very narrow depletion region.

- In tunnel diode, electric current is caused by "Tunneling".

- The tunnel diode is used as a very fast switching device in computers. It is also used in high-frequency oscillators and amplifiers.

- Leo Esaki observed that if a semiconductor diode is heavily doped with impurities, it will exhibit negative resistance.

#### Applications of tunnel diodes:

- 1. Tunnel diodes are used as logic memory storage devices.

- 2. Tunnel diodes are used in relaxation oscillator circuits.

- 3. Tunnel diode is used as an ultra high-speed switch.

- 4. Tunnel diodes are used in FM receivers.

- 5. Low voltage high frequency switching applications

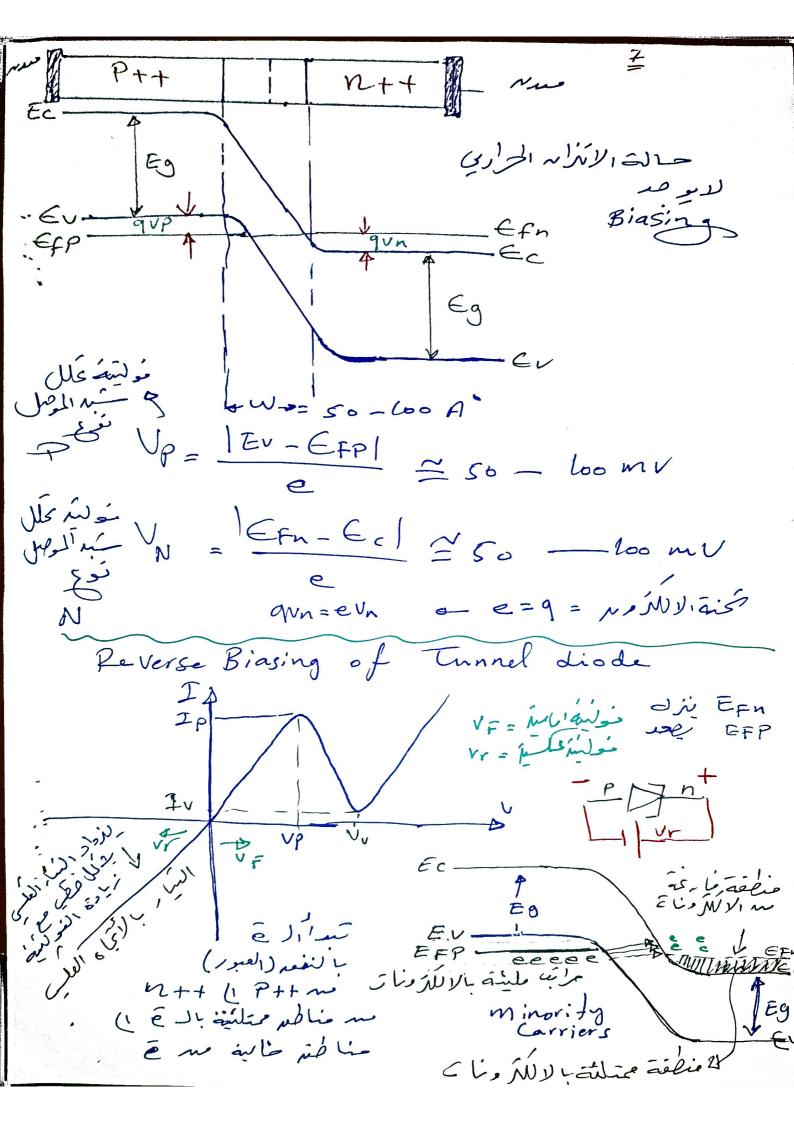

#### Basic of tunnel diode:

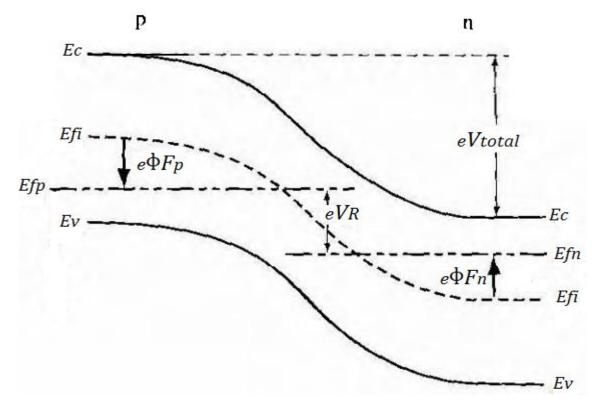

- ✓ The fermi level is constant throughout the junction. we notice that  $E_{FP}$  lies below the valence band edge on the p-region and  $E_{FN}$  is above the conduction band edge on the n-region.

- $\checkmark$  Thus the bands must overlap on the energy in order for  $E_F$  to be constant.

- ✓ It means that with a small forward or reverse bias, a filled state and empty state appear opposite each other, separated by the width of the depletion region.

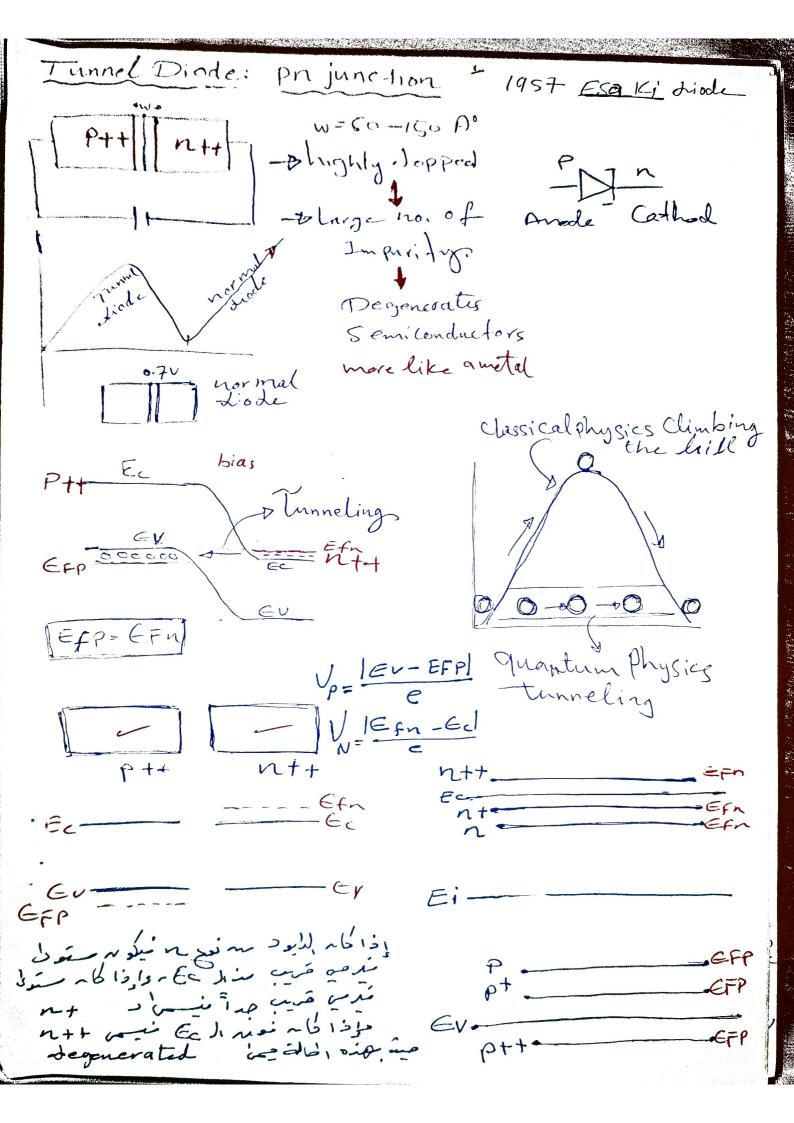

#### Basic of tunnel diode: (Forward bias)

A. When no voltage is applied to the tunnel diode, the conduction band electrons at n-side and the valence band holes at p-side are nearly at the same energy level.

But no electrons tunneling from n to p region. thus the net tunneling currents at zero applied voltage is zero

- B. When a small voltage is applied to the tunnel diode which is less than the built-in voltage of the depletion layer, no forward current flows through the junction. However, a small number of electrons in the conduction band of the n-region will tunnel to the empty states of the valence band in p-region. This will create a small forward bias tunnel current. Thus, tunnel current starts flowing with a small application of voltage.

- C. If the applied voltage is largely increased, the tunneling current drops to zero. At this point, the conduction band and valence band no longer overlap and the tunnel diode operates in the same manner as a normal p-n junction diode.

- D. If the applied voltage continues to increase largely, there are no electrons on the n side directly opposite to empty states on the p side.

For this forward- bias voltage, the tunneling current will be zero and the normal thermal current will exist in the device as shown in the **I–V** characteristics.

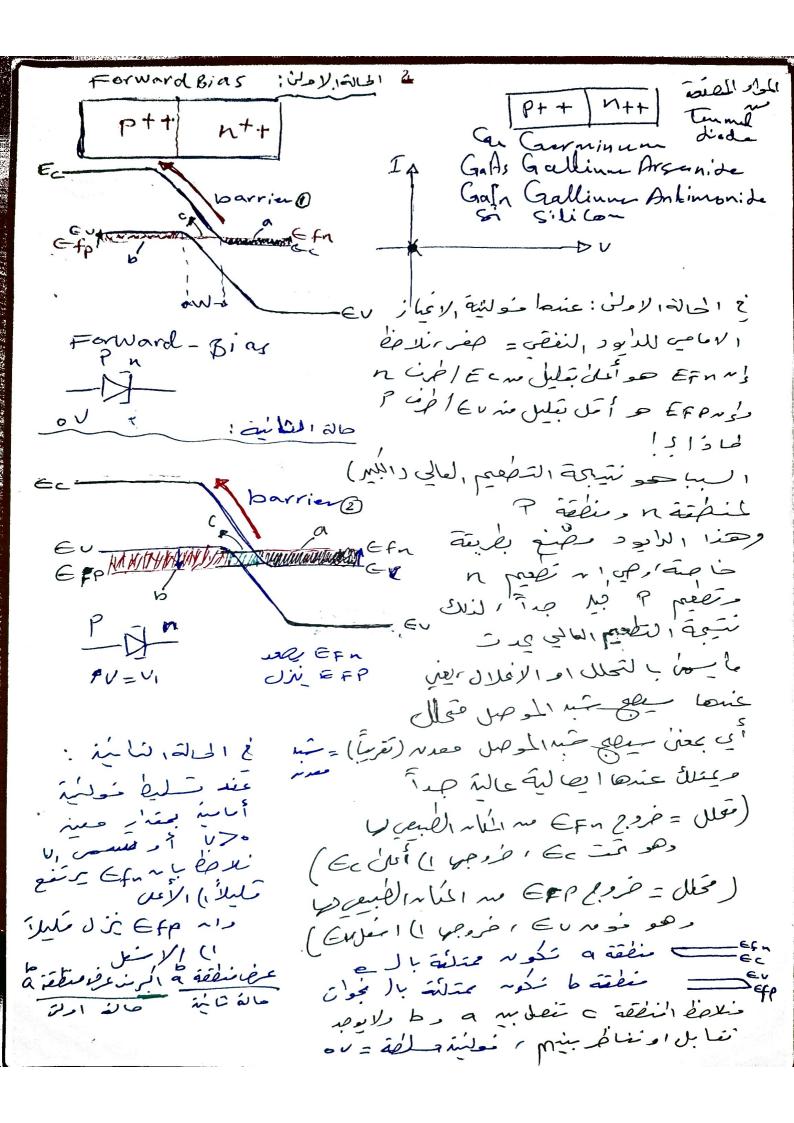

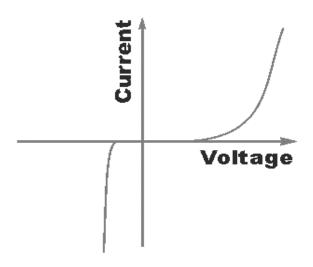

#### Back - word diode

#### **Definition of back-ward diode:**

- A backward diode is a form of tunnel diode where one side of the junction is less heavily doped than the other.

- This doping profile results in a diode that shares a number of characteristics with the tunnel diode, but modifies others. It means that in the reverse direction, the tunneling effect means that the diode has a characteristic similar to a normal forward biased PN junction diode.

- In the forward direction the tunneling effect is much reduced and it follows virtually the same characteristic as a normal PN junction diode.

Backward diode IV characteristic

#### Applications of Backward diode:

- 1. **Detector:** The backward diode provides a linear detection characteristic for small signals. Additionally the fact that there is no charge storage in its mode of operation means that it can be used for signals with frequencies extending to 50 GHz and more.

- 2. **Rectifier:** The diode is suitable for rectifying signals with peak voltages between about 0.1 and 0.6 volts

- 3. **Switch:** In view of its speed of operation, the diode is sometimes used for very high speed switching applications. It can be used as a switch within an RF mixer or multiplier where it provides excellent signal performance at microwave frequencies.

## **Lectures of Electrical Engineering Department**

Subject Title: Microelectronics

Class: 4th Electronic and Communications

|          | Lecture sequences:     | First lecture | Instructor Name: |  |

|----------|------------------------|---------------|------------------|--|

|          | The major contents:    |               |                  |  |

|          | 1- Backward Diode      |               |                  |  |

|          | 2-                     |               |                  |  |

|          | 3-                     |               |                  |  |

| Lecture  | 4-                     |               |                  |  |

| Contents |                        |               |                  |  |

|          | The detailed contents: |               |                  |  |

|          | 1- Working principle   |               |                  |  |

|          | 2- Characteristics     |               |                  |  |

|          | 3- Applications        |               |                  |  |

|          |                        |               |                  |  |

Backward diode الثنائي العكس so metal Conduction الحادا سمع بالنائي العاسى ٦ لأنه لجل بالاخياز العلس. Rectifier -; Élia), in a chim! Switch Detectors رمز الثنائي:-ر من الشائي العالي Band diagram of backward diode. n+ P++ nt pul esse EV-EFP ---Qual tum Tunneling unbiased EV Reverse Bias in EV Je 1 OP EFP IN LIP BON' ail ited the lies relip Pill n'y ? Piell Piel EV cie, 1 (Serg mã 4 (4+9) 121 Jes (8) Eccipistor Hell de I die Jako EFN JI Los & als } awall an niebl is in it is the Ec المكسة الما أدي ال نقابل مع ط وبالثالث عبور م عظتم لطورة عالية (nt) الم يتول

backward diode (also Called back diode) ? braving a better Conduction for Small reverse biases (for example -0.1 to -0.6 V) than for forward bias voltage. backward 11 Node مين مد س かんかいししいか Zoner diode S cas Tunneling JI مُولِيْهُ مُلْدِلُهُ لَمُ 4 m i as 121 dus (++9 va Backword ) you goil ! The rule side and co ( مين منملة) موبالنالي قيت Unneling raid l'alles (backword) g'u, lip & in bol and in liel 13} Tip out over the conting) reil sab ~ 6 ر سائ عنه ها منا ، لنائ لاي غ صالة ، لايما ; بالرتماه لاماع) رين شيك الأنشار فالما كال سنا عده الانماز العلى مؤلَّ فع الله المار العلى على و العند 1 arep i ( ) ! è l > b . a (P Tiele (n Tiele mo = is Will ) = e) م بالنتجة نام خواص إلى - الغولية كون الكان م المال عناز الليام الرعناز الليام م عابهة كون م Zonor diode J' العال العال back ward

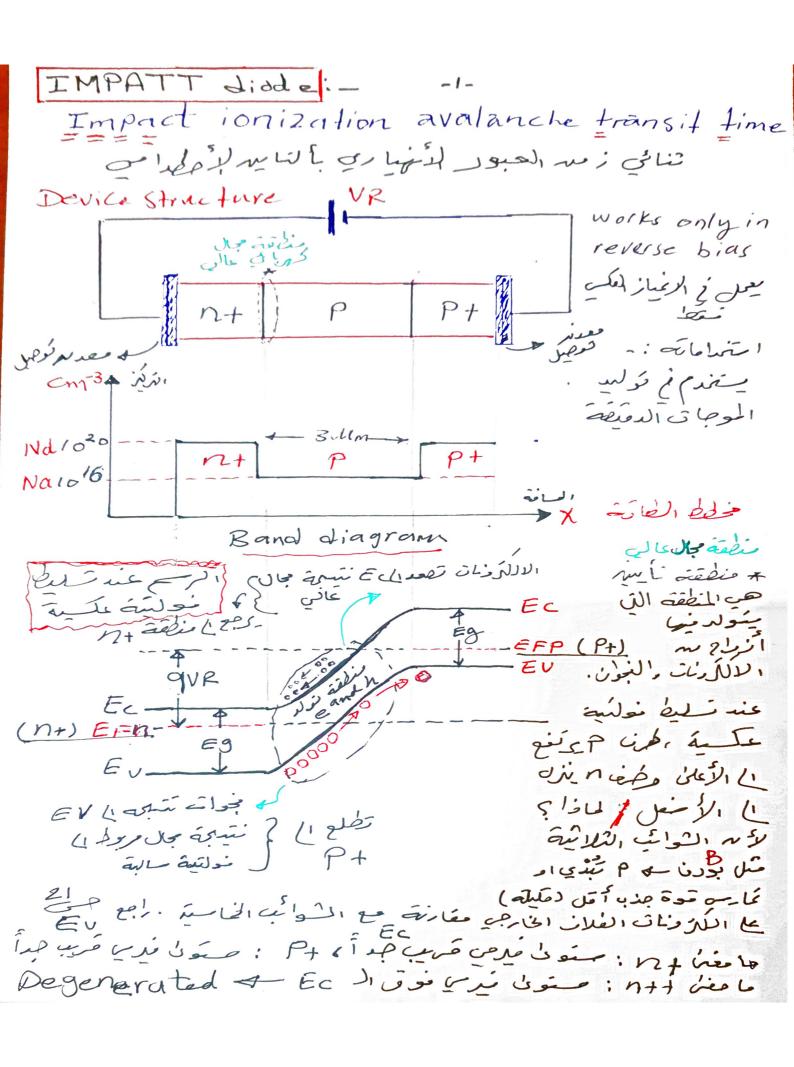

# **Lectures of Electrical Engineering Department**

Subject Title: Microelectronics

Class: 4th Electronic and Communications

|          | Lecture sequences:     | First lecture | Instructor Name | : |

|----------|------------------------|---------------|-----------------|---|

|          | The major contents:    |               |                 |   |

|          | 1- IMPATT Diode        |               |                 |   |

|          | 2-                     |               |                 |   |

|          | 3-                     |               |                 |   |

| Lecture  | 4-                     |               |                 |   |

| Contents |                        |               |                 |   |

|          | The detailed contents: |               |                 |   |

|          | 1- Working principle   |               |                 |   |

|          | 2- Characteristics     |               |                 |   |

|          | 3- Applications        |               |                 |   |

|          |                        |               |                 |   |

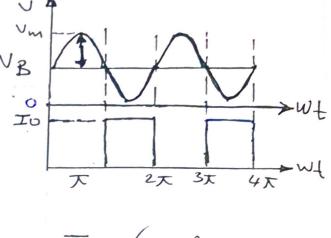

Efficiency: 4:

2 ilp Power = UB x 10 ادا متعالی 2: لأسموجود فلال فغالع علی المعالی فغ

of = ac oil power

30 po de mo

ac of power

$$= \frac{1}{T} \int U_{ac} I dQ = \frac{1}{2\pi} \left[ \int v_{m} s_{in} w_{t} + \int I_{o} v_{m} s_{in} w_{t} \right]$$

$$= \frac{1}{T} \int U_{ac} I dQ = \frac{1}{2\pi} \left[ \int v_{m} s_{in} w_{t} + \int I_{o} v_{m} s_{in} w_{t} \right]$$

$$= \frac{1}{T} \int U_{ac} I dQ = \frac{1}{2\pi} \left[ \int v_{m} s_{in} w_{t} + \int I_{o} v_{m} s_{in} w_{t} \right]$$

$$= \frac{1}{T} \int U_{ac} I dQ = \frac{1}{2\pi} \left[ \int v_{m} s_{in} w_{t} + \int I_{o} v_{m} s_{in} w_{t} \right]$$

$$= \frac{1}{T} \int U_{ac} I dQ = \frac{1}{2\pi} \left[ \int v_{m} s_{in} w_{t} + \int I_{o} v_{m} s_{in} w_{t} \right]$$

$$= \frac{1}{T} \int U_{ac} I dQ = \frac{1}{2\pi} \left[ \int v_{m} s_{in} w_{t} + \int I_{o} v_{m} s_{in} w_{t} \right]$$

$$= \frac{1}{T} \int U_{ac} I dQ = \frac{1}{2\pi} \left[ \int v_{m} s_{in} w_{t} + \int I_{o} v_{m} s_{in} w_{t} \right]$$

$$= \frac{1}{T} \int U_{ac} I dQ = \frac{1}{2\pi} \left[ \int v_{m} s_{in} w_{t} + \int I_{o} v_{m} s_{in} w_{t} \right]$$

$$= \frac{1}{T} \int U_{ac} I dQ = \frac{1}{2\pi} \left[ \int v_{m} s_{in} w_{t} + \int I_{o} v_{m} s_{in} w_{t} \right]$$

$$= \frac{1}{T} \int V_{ac} I dQ = \frac{1}{2\pi} \left[ \int v_{m} s_{in} w_{t} + \int I_{o} v_{m} s_{in} w_{t} \right]$$

$$= \frac{1}{T} \int V_{ac} I dQ = \frac{1}{2\pi} \left[ \int v_{m} s_{in} w_{t} + \int I_{o} v_{m} s_{in} w_{t} \right]$$

$$= \frac{1}{T} \int V_{ac} I dQ = \frac{1}{2\pi} \left[ \int v_{m} s_{in} w_{t} + \int I_{o} v_{m} s_{in} w_{t} \right]$$

$$= \frac{1}{T} \int V_{ac} I dQ = \frac{1}{2\pi} \left[ \int v_{m} s_{in} w_{t} + \int I_{o} v_{m} s_{in} w_{t} \right]$$

$$= \frac{1}{T} \int V_{ac} I dQ = \frac{1}{2\pi} \left[ \int v_{m} s_{in} w_{t} + \int I_{o} v_{m} s_{in} w_{t} \right]$$

$$= \frac{1}{T} \int V_{ac} I dQ = \frac{1}{T} \int V_{ac} I d$$

AC OIP POWER = - IOVIM

2 = 2 Vm × 100%.

Vmlmax) [56 hpi vis Vm (max) = 3 VB

الاشارة الله بالأفراج تدل: ع الم الليود مولدللفررة لوكانة الاكراة + معناها اللود ستولك للعدرة

عادة الانوفي اشارة الالك في عادون النفاءة (محل).

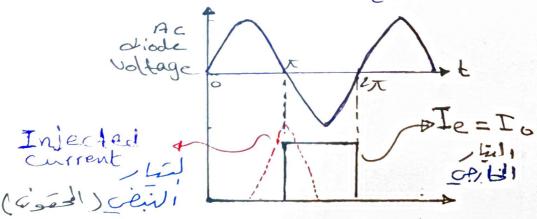

Induced External Current: The work done on the positive charge is: مانة قراكي عي مافة أول \* قوة الما مه الله تعامل Wh= F \* X -D مراب المنفولات في المنفولات المنفول Where The Force F = 172 P+ 122 P+ F = Q+ x Eo -2 apod aismilities of Noils ap @ Elses lenz law and The Electric field = العجال ير خولنية E. Vo الأسمع كانوس The dc power supply does العولية والذي يا دي work in transferrings the المامة عند عندلية charge & through the external circuit which is given by: V = Exb :. external & Vo \*Q ->Q : E = ~ الشمنة المنتدلة إلى الأو له الشغل للعدر الخارجية We= papel ¿ jeil jein, يسامي الشغل المجنز في نقل الفيوات داخل السُمِحة ( Wh ) as (4) asles عًا فعد المعلية V= -That's mean We = Wh J= vi? = W

We=Wh \_\_\_ Odsles=@ables

QEOX = VQ

Q+VX = XQ

= = = =

airmit and Q = Q+ X

Coincid and D

Ie = external current

Io = output contrent

Ie = Io

$$\frac{d\bar{Q}}{dt} = \frac{Q^{\dagger}}{W} \frac{d\chi}{dt}$$

$$\frac{d\bar{Q}}{dt} = I_{e=1}$$

نشعة الطريس من أوجد السار الخارجي

$\frac{dx}{dt} = V_S \quad \text{old sind as } m = 10^{\frac{1}{2}} \frac{Gm}{sec}$   $\frac{1}{3} = \frac{1}{2}e = \frac{Q^{\frac{1}{2}}}{M} V_S$

In = Ie = The current in the External circuit.

Examples Consider a Read Diode With W= Sum, Vs = 107 cm and a Valanche-Denerated number of holes = 6×10 holes or Cohorge). Deturning the induced external current and the frequency. Solution:

The total the Charge generated by the avalanche multiplication process is:

$Q^{\dagger} = 6 \times 10^{7} \times 1.6 \times 10^{-19}$   $Q^{\dagger} = 6 \times 10^{7} \times 1.6 \times 10^{-19}$   $Q^{\dagger} = 9.6 \times 10^{-12}$  Coul. (c) [3]  $Q^{\dagger} = 9.6 \times 10^{-12}$  Coul. (c) [3]

Io i Je=192 mA op, il, in,

$$\int = \frac{V_s}{2W}$$

$$\int = \frac{167}{2\times 5\times 10^{-4}}$$

--- f=10 GHZ

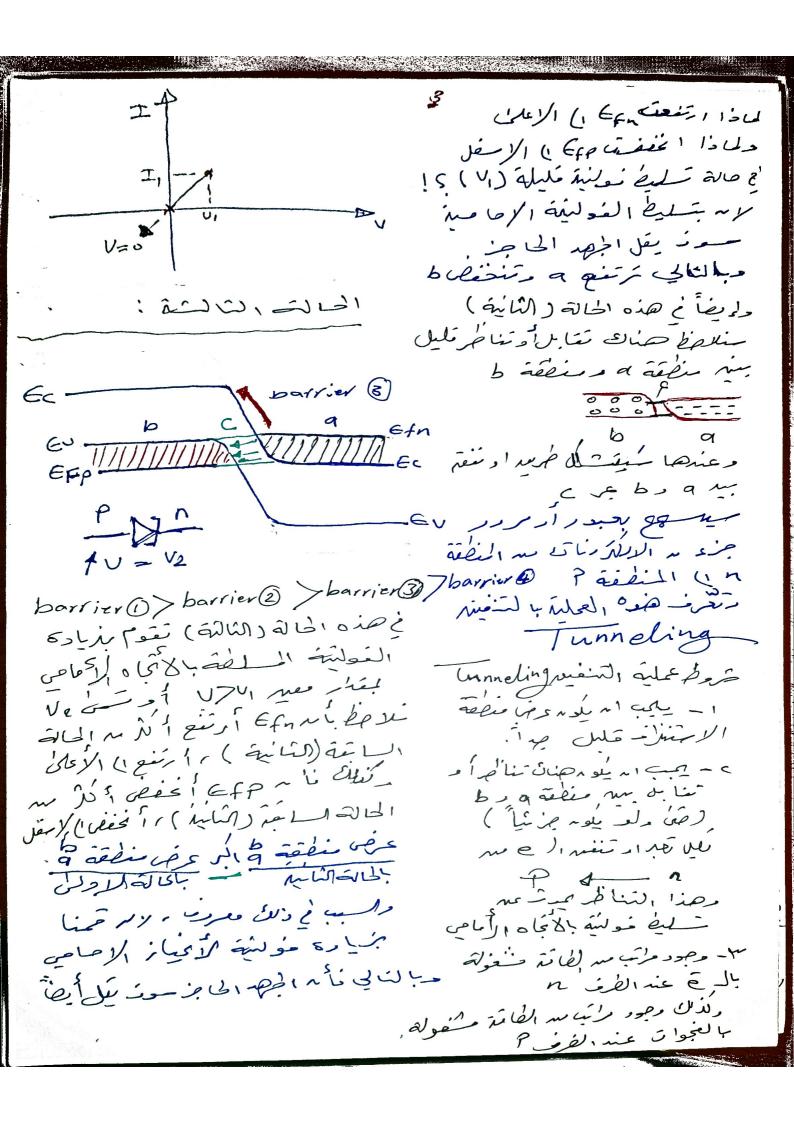

## Operation Mechanism: a Libeliup ist

في منطقة ابجال الدرج باتي العالمي و رالتي منطقة المراح العجوة العجاز : يعني منطقة المراح العجوة العجاز : يعني منطقة المولار وم عدا لعجوة مولاً زوجاً سه الر ( + + ) - مركوم طاقة هذا العدلار و في الدركة و النجوة عالمية وعندها مقطوع هذه الدلار و النجوة عالمية وعندها مقطوع هذه الدلارة و النجوة عالمية وعنده المولارة هذا بالذرائ الافرائ و النجوة عالمية المولار للذرة المولارة هذا الموالي المولارة المول

۱- فدرة عالمية >- تزود عالي بدود 366HZ

\_: autel, sie o unt m

المنولتية العلمة اللامة مجاد في الات ارة الما يكروي المؤلاة المن عدث المنولتية الله على الفولتية اللي عدث المنولة الله عد الموليا ر للنداخ جيث تفعل العلما عد الديمام المنولتية بالمناج عد المولية بالمولية المنولتية بالمولية المنولتية المنولية المنولتية المنولية المنولة ال

Break Down Voltage , hill air in com dis Ionization Voltage in li, Einstein ie 1 2mi i adose لافا يدم عدنان هذه العلية لا النا بف الترسوري high noised - whe she is and لا م عدت بدن عدما على مر دد عالی لشایت) لا مِنْ سِ يَعَدُ سِكُل بِهِ عِلْمُ اللهِ عِلْمُ اللهِ عِلْمُ اللهِ عِلْمُ اللهِ عِلْمُ اللهِ عِلْمُ اللهِ عِل Electric field in En adie العجال المدحرباعي (e-h) إن معظم الازراج (h- e) تَولد في منطقة الحيال النظر الى العالي أي في المنطقة Enero < X Losum أن الحال اللهربايي ك E>3×105 V/cm مالاللادنات للنولدة تنتفل فورآ الم منطقة + ١١ ١ ما الثقوب x (um) المتولدى با نها تفي عر منافقة م  $\epsilon_c$ 45 EL-0 20 JUS Pt deen L 20 Jes EC> 3×16 ~ و لیے 3 for Si سر جوراط 2 الطاقة 9VR Hum) إن العقة للنفرقم لحسه وجول النفوب عظ منم الفانة عند الاربياء M'il séeir mas les Ptaées L' OVR (EFF- EFN) عد ٩ سے أو يولف ناخر زمر لعبور

Transit time delay i see it is in عدفة : ماغة , لايباء بدرد سيده والأنعة صم. قد ع ميسة الجال الرهم الح العال الحال الحال الحديد عنفة Critical Electric Field. ملافقة : إن النبعات المتولدة في منافقة الربيار عَمَاح ال رس Pt älie Le Vetel Pailie 1920 مرفعا مَلْ أس لعبور فكا زأر الأول للإث رع المتولية رىعير الذس كا لغولية المسلقة بميث تناسب تناسب على مع المؤلية الملكة إذاً مناسب مُردد الإطارة المنولة فردياً مع الفولية المسلفة (العالمية) علامضة: أحذنا بنظ الاستار زير العبور للعبوات مق الغجوات س منافقة الربيار دالما سي الم P rs P+ zaéin 15 e / en mi , til lei ist / " لاله الاللامات ما عناج رس للعبور النام : de l'électrors de l'électrors The way is n+ aelie ( ani si hu. ناوعة : عناما رجبع الجال الأهربان ع ما وياً للعز ( تا عندها سوف تعل سرعه الحاملات والعجوات ) ولحل هذه الحيكة: مُ رَجُور وي س بنية المايود CNINC 14 Ser

Read Dide - ¿m ( ¿ Éll) som viste bis. Jani protes della più più dot: Read platino عرب ق دمنیقه سه فعله عله معله علی ما نعبان الکورانی Impatt Read Look - suit i april, .id هذه البلطة الجديدة أو الديد مؤلف مد i = Intrinsic ciones de les (hus = eur)Thrinsic (classic) (classic) مس تم عام هذا العالم بتعقيم النافقة الومصة م الما العالم بتعقيم النافقة الومصة م الما الما المنطقة الموالي في المنطقة الموالي في المنطقة الموالي المنطقة الموالي المنطقة الموالي المنطقة المن ذات النفعيم الجوهري تعريباً مشبه موهل نفي (مجوات الرسم) NA5\*10'6 (e+h) which is about the constraint of the const Na1613 53EA J. = EC

No = Ecb + W [Ec -  $\frac{e(2S) \text{Nia}(P+)}{Es}$ ]

The interpolation of eccount of the state of the

مرعفة: - -8-العندسة المتناءبة (الاحفال) عن نشيجة هجود ثنائي ولا(العلل) يُ دائرة لهوم ت دفيقة العني هذه الفولية المتناورة المركبة فَوَى الْفُولَيْةُ اللَّهُ عَلَى (VB) هي سر منوليةُ اللَّذُى الربوطِ

برا الثنائي. بلاطهة: - ي منفقة الانهار (السُهوري) تنوّلد مجوات واللرفات -7- avor 2001 de 200 cie c

نتهة ط المخوات موهنه العجوات سوف تتحرك وتم فل منطقة الأنجراف متجرهة كو الطف +

أسا الدلكة من المتعلمة من منافقة التأسير لم نقم برسول مون سَجه کو اللاب + ۸،

عندما تعبي النولية المتناوية موجبة ، تفاف الداد جديدة مسرا لثقوب المنولاة ما منافقة (الربيار أو النبهور) ، وكما (b ālei) - 7 ased ¿ ādeisi bebs! in مرتسقر الثقدب بالزيارة ما دام الجال اللربائي أعلى مس Ec حبذلام فأم الثقوم على) الذروة ليس عد 12 مي العنولين عند العنول بل عند بل عند بل عند عند العنول عند العنول عند العنول عند العنول عند العنول العن 10 500 Eliais 17 aser 2 pm Eini- : Edple مبدلك يكوم منالك كوليدللفدرة ، و نتيجه له التقلبات العثوالية علية النظا عنى السهوري للدم العواماء كالهة

W aild gées (5's el jai sée la Jule la vij à dép le رهي طول منطقة الاستثنان على للفف المال للذين ( دلعند الماريظوري لنعف الساب مسالع مف 19.ed, mi) tr = 1/2 T , T = 1  $\pm r = \frac{1}{2} \frac{1}{f}$ W= -il Us= = sidiaes of  $tr = \frac{\omega}{U}$   $\frac{\omega}{U} = \frac{\omega}{U}$ Vs=sliny as ~ y as = as wi Vs = 107 cm for Si  $w'' = \frac{\hat{a} \cdot \hat{b}}{\hat{a} \cdot \hat{b}} = \frac{w}{v_s}$  $\frac{W}{Us} = \frac{1}{2f} \cdot 2f W = Vs$ --- f = Us نترة مؤليه النجواة نترة نعل الفنوات

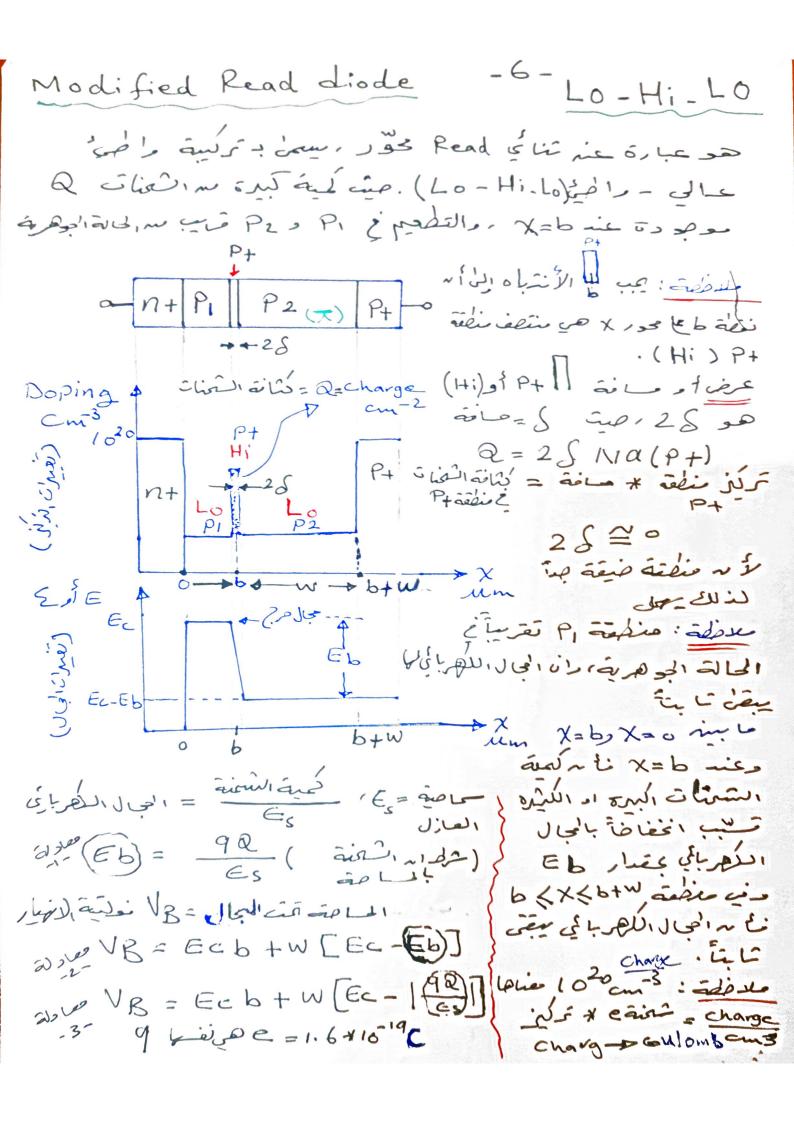

ملاطف : العا منة السالية العن تع لير (للعكرة).

Example: IMPATTOSIC OP EW, 2011, apt  $F = \frac{\sqrt{5}}{2W}$   $W = 2 \frac{1}{\sqrt{10}} \frac{1}$  $f = \frac{107 \text{ cm}}{2 \times 2 \times 10^{4} \text{ cm}} = \frac{10''}{4}$   $f = \frac{\text{cm}}{\text{sec}}$   $f = \frac{\text{cm}}{\text{sec}}$   $f = \frac{\text{cm}}{\text{sec}}$ More than us f = 25 GHZ  $W = \frac{1}{2} \frac{1}{$ Example: install 513 Lo-Hi-Lo relle singi  $b = 1 \mu m \qquad (P_2 = \pi) \qquad P_1 + P_2 p_1 + \pi p_1$   $W = 5 \mu m \qquad (P_1 = P) \qquad Lo Hi \qquad Lo$   $(VB) / Lip M = 2 + 10^{12} \frac{\text{charg 2ib 15 Li}}{\text{cm2}}$ Talien ade 13! Impatt élül sos les Eptil sélet Dies de l'aile deb mm 1 sals délis 1 seul EC-EL

WHE

WHE

WE CONSTRUCT THE SECRETARY STATES TO SECRETARY TO SECRETARY STATES TO SECRETARY TO SECRETARY STATES AND SECRETARY STATES AND SECRETARY TO SECRETARY STATES AND SECRETARY SECRETARY STATES AND SECRETARY SECRETAR Ec= V = 33V = 3.3 x 18 Yam VB=Ecb+[Ec-(92)]WEb VB = 33 + [3.3×105 1.6×10 ×2×10 ]5×104 JB = 33+13 = 44V J = 33+13 = 44V 100 = 100 GHZ 2\*5 × 10-4

## **Lectures of Electrical Engineering Department**

Subject Title: Microelectronics

Class: 4th Electronic and Communications

|          | Lecture sequences:     | First lecture | Instructor Name | : |

|----------|------------------------|---------------|-----------------|---|

|          | The major contents:    |               |                 |   |

|          | 1- BARITT DIODE        |               |                 |   |

|          | 2-                     |               |                 |   |

|          | 3-                     |               |                 |   |

| Lecture  | 4-                     |               |                 |   |

| Contents |                        |               |                 |   |

|          | The detailed contents: |               |                 |   |

|          | 1- Working principle   |               |                 |   |

|          | 2- Characteristics     |               |                 |   |

|          | 3- Applications        |               |                 |   |

|          |                        |               |                 |   |

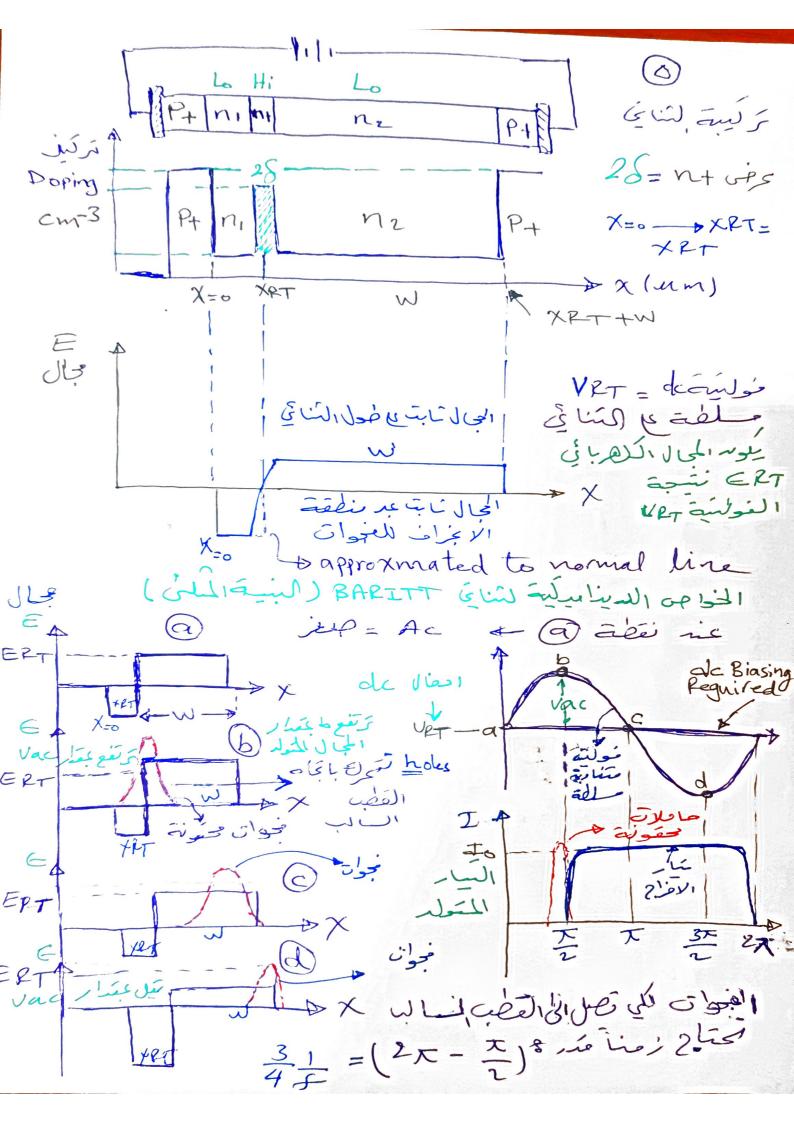

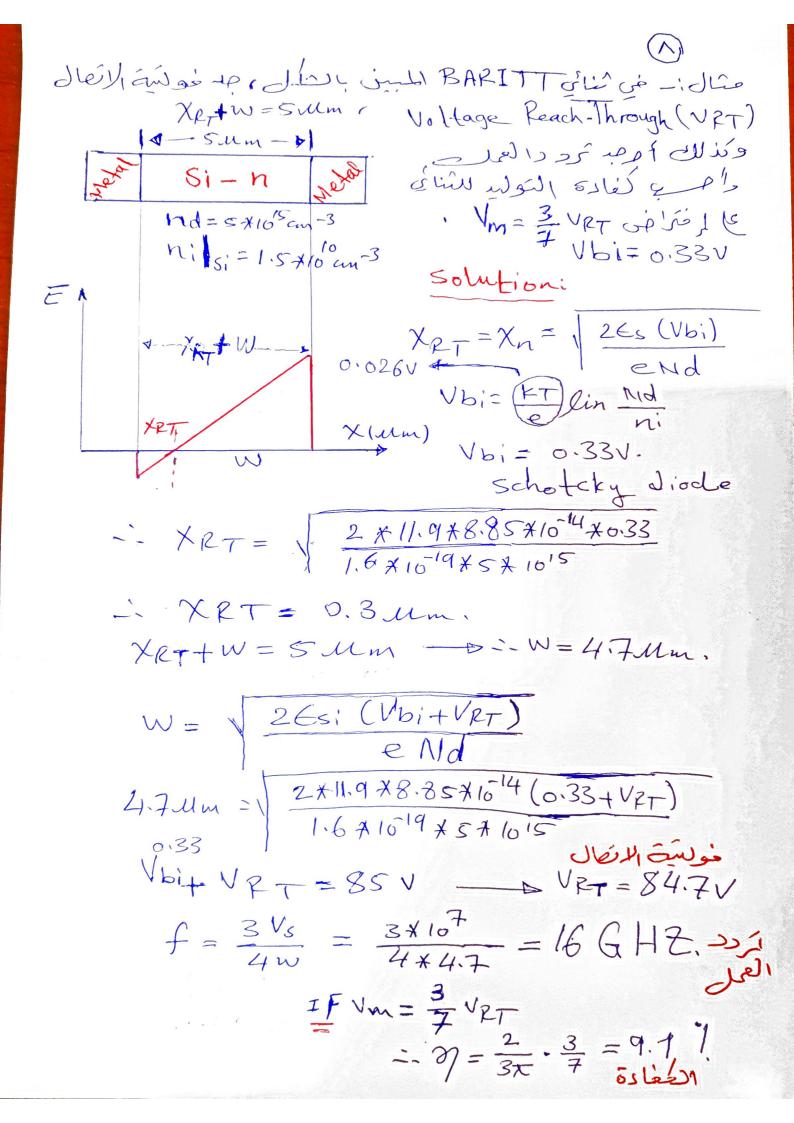

BARITT Diode BARrier Injection Transit Time Diode منائی زمه العبور عند الحقه خلال الحاجن.

\* \* \* \* بحل علی مولید صوع مت دعیفة

\* الدلید الحسولات علی می هذا

الدنائی تعتمد علی الحقید الترصوایونی (ایونان متولدة بالحراق)

الدنائی تعتمد علی الحقید الترصوایونی (ایونان متولدة بالحراق) ٥ والمنكار الحاملات مهي العبوات الحدم: عبر عامز جهد أدر ( مجد ما جن ) ، وسم خلال منافحة إلى إن العامة عبور الحاملات). وعلی الرس فی عبور هذه الحاملات الله نظراً لعم معود النفاعف الربياري (السجوري) نا - الطوفاء كور فللة إوبالقابل تكور الندرة علیات، ربالنالی تکویر اللفادة کوئول علی فی صالح اله AATT . المرابع الأولما للمولما و ها الذا عن الأولما للمولما و المالية للمالية المالية المالي خيا إلى قال والله الماري الوالمنة (Local oscillators = add 154 in ilb) (Doppler detectors Mos ie 6) ملاحظة: تكور الفدة عليك ربعني العدرة الى رجة علية ملاطفة: دكور الضوضاء أقل في عملية الحسر الترسوابوي معارنة مع الضوضاء في عملية التأسر الإططاعي. (shop) BARITT < IMPATT (shop)

Device Structure: Their sli M= Metal vue n-si=ntype sili con M n-s: M of his del be dead in ? ~ 6 BARITTERPY JE بالمقام الدكيب انزام مذي معدم - مشم موص - معدم M S; - M • (سس) عو وهذا الثنائي هو ا به المجال عدما ۲۶۲ العجوات عدما ۲۶۲ العجوات الأساس عبا ١٥٠ عد ثنا ئيس سد نوع شوتکی دایو د XPT= Ossil mes Jolis عربوطسر با لتعاكب ور م الجال عند ما الانعار ٢٦ الح ع الله تسب الحقيد هذه العلية عي المراد الحسر المائة المعام المردداد الحسر المائد المعسر المردداد المعسر المعسر المعسر المردداد المعسر المعسر المردداد المعسر المعسر المردداد المعسر المردداد المعسر المردداد المعسر المعسر المردداد المعسر medi ei للغوات المناده عرب المناده الحميم Energy Band Diagram. عافظة: يعدانت رالحاملا و دالبواى كار الجهد الحالم بایناز احام ولیس عکس ، برب صورت دا بور رجم \_1\_ مماز باعبار اطامی

عنفقة النول ( الحسر ) للغبوات المي المفاقة : عفونه التي سية عندها الحال الهرباي بالإزديا و(XRT) معرفة اعتما ملقنا خولية عي الثنائ وكانت فيميا TyV=V, veri c'll!: Lleis elis ne ت ابن أو تأض الجال السالب مع المجال الموجب · [ & 1 / ) [ ] @ Exis :- علية تعابل الجالد خورية لحددت الحد الرسوايوي مردلك سيف العولية الماعة لوجول المتابل برج V VReach Through Forward and Reverse field are Inter leaved. 1) NI ship well 18in A VET I'M is .: alose معد ا عقان العجوات في منافقة الحقم المعوات عن منافقة الحقم (XRT) مَنكون عَللَة ؟ ليادًا ؟! را مر الجال المعرائ من منطقة الحقيديان وافي على منطقة الحقيديان وافي على مناع المعراد المعرد المعراد المعراد المعراد المعراد المعراد المعراد المعراد المعرد ا M Si-n M Si-n M Si-n M Si-n M ينون على الحال الكر دعين ( @ sied ) Liet iet

TRY USY I neier Eiser of the ser i adip the med le de pol mi i sel entrope of the de lay time of the ser i it line of the transit de lay time of the circle

لأجر تقليل الغولية المسلمة على بال كوبا في كافي المن الأونى على الدين الحاول على بجال كوبا في كافي من منطقة الابخان المحاول على محال كرائلي لثنائي من منطقة الابخان المعاول على منطقة الابخان لثنائي المبنية المائلي لثنائي على المبنية المائلي لثنائي على المستمنات قو جدعنه نقفة المقد ، ويب المستمنة وحوقعها عجدد لومنال) المستمنة وحوقعها عجدد لومنال) بشكل مناهب لفاء تقليل الفولية المسلمة المائل من من بشكل مناهب لفاء تقليل الفولية المسلمة المنافي لا يعاد والحالال على المجالة والحالال على المجالة والحالال على المجالة والحالال على المجالة المنافية المناف

| + a P+ | n, nt | n <sub>2</sub> | P+         | 0 |

|--------|-------|----------------|------------|---|

| , ,    | ,     |                | III Milian |   |

ابد المبدأ الاسام لهل هذا الدابود مشابة لمبدأ على شنائي TMPATT و من هناك فرقاً بمباسباً وا فرآ وهو من شنائي منهوري (انهاري) وهو من شنائي المحقونة هي متروا يونيا يُول من الحاملات المحقونة هي متروا يونيا يُول من الحاملات المحقونة هي متروا يونيا يُول من الحاملات المحقونة هي متروا يونيا يُول من المحاملات المحتوانية المحتو

copalisis existification (O aries) Exis (ننطة طحه) منإى الشوب الحقونة الأوال النولية المناوبة الوناوية الذروة ني عدد الثقوب الحقونة عندا تجل الفولنة الى فيها القوى. مانعة: نادمة ( معت ٥) أفي الرا الحالات العالمات العقولة على العالمات العقولة على العالمات العقولة الع Lei vie l'hel es lléelie libiler الفوات ملى تصل إلى الحق السانة التي المانة التي المانة التي والمانة التي المعرة الماملة ، والمانة التي المعرة الماملة المرة الماملة المورة ال 3 = W = 3 + 1 3 = Vs  $\pm r = \frac{w}{v_s} \qquad \therefore f = \frac{3}{4} \frac{v_s}{w}$ ولذلك فقط في مسالدرة هنا لا كان اللي هو ابع دورة de power = 3 To V2T ac power = 1 2 To Sin Wt d(wt) Vm = VRT - 2 LVRT ac power = 1 [ S IoVET sin we dut + S IOVET 2 Sin we dut + S IOVET 2 Sin we dut]

# **Lectures of Electrical Engineering Department**

Subject Title: Microelectronics

# Class: 4th Electronic and Communications

|          | Lecture sequences:                              | First lecture | Instructor Name | : |  |

|----------|-------------------------------------------------|---------------|-----------------|---|--|

|          | The major contents:                             |               |                 |   |  |

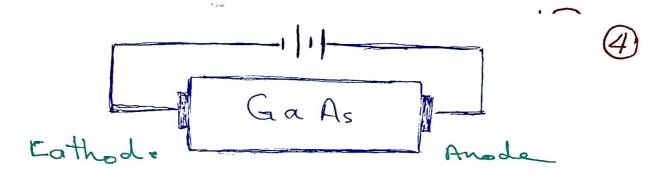

|          | 1- Transferred Electon Device TED or Gunn diode |               |                 |   |  |

|          | 2-                                              |               |                 |   |  |

|          | 3-                                              |               |                 |   |  |

| Lecture  | 4-                                              |               |                 |   |  |

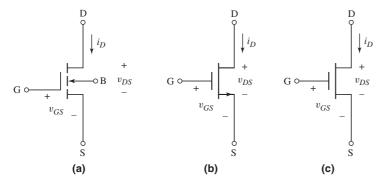

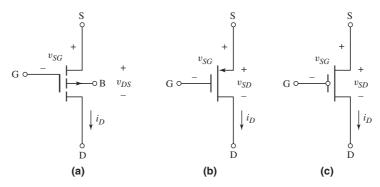

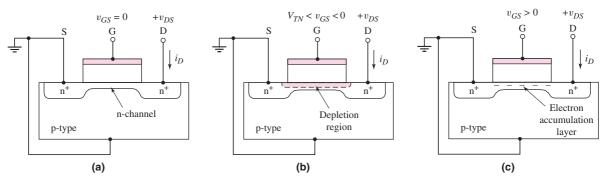

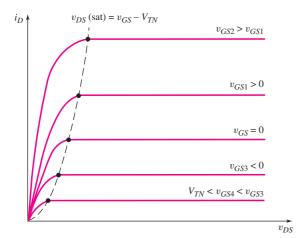

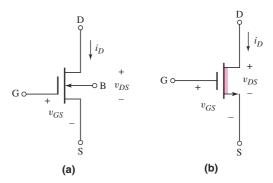

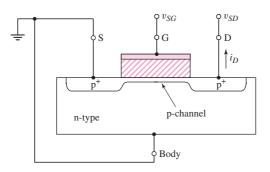

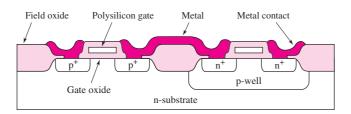

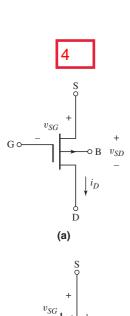

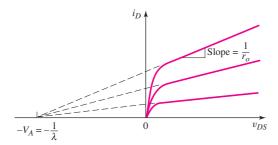

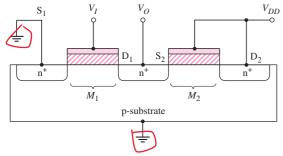

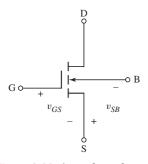

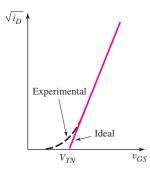

| Contents |                                                 |               |                 |   |  |