# **Digital Circuits - Multiplexers**

# **Multiplexer**

is a combinational circuit that has maximum of 2<sup>n</sup> data inputs, 'n' selection lines and single output line. One of these data inputs will be connected to the output based on the values of selection lines.

Since there are 'n' selection lines, there will be 2<sup>n</sup> possible combinations of zeros and ones. So, each combination will select only one data input. Multiplexer is also called as **Mux**.

## **4x1 Multiplexer**

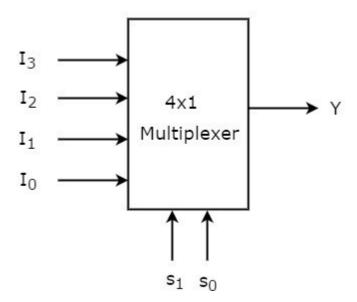

4x1 Multiplexer has four data inputs  $I_3$ ,  $I_2$ ,  $I_1$  &  $I_0$ , two selection lines  $s_1$  &  $s_0$  and one output Y. The **block diagram** of 4x1 Multiplexer is shown in the following figure.

One of these 4 inputs will be connected to the output based on the combination of inputs present at these two selection lines. **Truth table** of 4x1 Multiplexer is shown below.

| Sellect        | Outp<br>ut |                 |

|----------------|------------|-----------------|

| S <sub>1</sub> | <b>S</b>   | Y               |

| 0              | 0          | II <sub>0</sub> |

| 0              | 1          | II <sub>1</sub> |

| 1              | 0          | II <sub>2</sub> |

| 1              | 1          | II <sub>3</sub> |

From Truth table, we can directly write the Boolean function for output, Y as

$$Y = S_1 \cdot S_0 \cdot I_0 + S_1 \cdot S_0 I_1 + S_1 S_0 \cdot I_2 + S_1 S_0 I_3$$

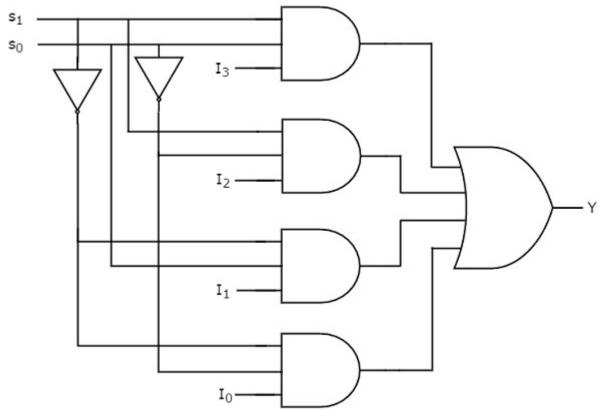

We can implement this Boolean function using Inverters, AND gates & OR gate. The **circuit diagram** of 4x1 multiplexer is shown in the following figure.

We can easily understand the operation of the above circuit. Similarly, you can implement 8x1 Multiplexer and 16x1 multiplexer by following the same procedure.

# Implementation of Higher-order Multiplexers.

Now, let us implement the following two higher-order Multiplexers using lower-order Multiplexers.

- 8x1 Multiplexer

- 16x1 Multiplexer

## 8x1 Multiplexer

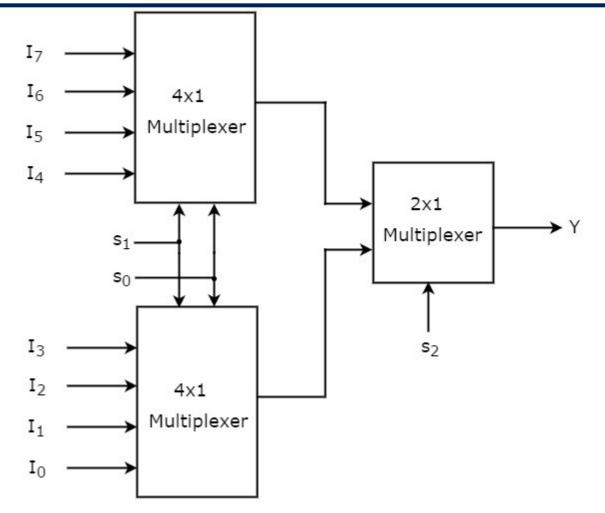

In this section, let us implement 8x1 Multiplexer using 4x1 Multiplexers and 2x1 Multiplexer. We know that 4x1 Multiplexer has 4 data inputs, 2 selection lines and one output. Whereas, 8x1 Multiplexer has 8 data inputs, 3 selection lines and one output.

So, we require two **4x1 Multiplexers** in first stage in order to get the 8 data inputs. Since, each 4x1 Multiplexer produces one output, we require a **2x1 Multiplexer** in second stage by considering the outputs of first stage as inputs and to produce the final output.

Let the 8x1 Multiplexer has eight data inputs  $I_7$  to  $I_0$ , three selection lines  $s_2$ ,  $s_1$  & s0 and one output Y. The **Truth table** of 8x1 Multiplexer is shown below.

|          | Outp<br>ut |          |                 |

|----------|------------|----------|-----------------|

| <b>S</b> | <b>S</b>   | <b>S</b> | Υ               |

| 0        | 0          | 0        | II <sub>0</sub> |

| 0        | 0          | 1        | II <sub>1</sub> |

| 0        | 1          | 0        | II <sub>2</sub> |

| 0        | 1          | 1        | II <sub>3</sub> |

| 1        | 0          | 0        | II <sub>4</sub> |

| 1        | 0          | 1        | II <sub>5</sub> |

| 1        | 1          | 0        | II <sub>6</sub> |

| 1        | 1          | 1        | II <sub>7</sub> |

We can implement 8x1 Multiplexer using lower order Multiplexers easily by considering the above Truth table. The **block diagram** of 8x1 Multiplexer is shown in the following figure.

The same **selection lines**,  $s_1$  &  $s_0$  are applied to both 4x1 Multiplexers. The data inputs of upper 4x1 Multiplexer are  $l_7$  to  $l_4$  and the data inputs of lower 4x1 Multiplexer are  $l_7$  to  $l_9$ . Therefore, each 4x1 Multiplexer produces an output based on the values of selection lines,  $s_1$  &  $s_9$ .

The outputs of first stage 4x1 Multiplexers are applied as inputs of 2x1 Multiplexer that is present in second stage. The other **selection line**,  $s_2$  is applied to 2x1 Multiplexer.

- If  $s_2$  is zero, then the output of 2x1 Multiplexer will be one of the 4 inputs  $I_3$  to  $I_0$  based on the values of selection lines  $s_1$  &  $s_0$ .

- If  $s_2$  is one, then the output of 2x1 Multiplexer will be one of the 4 inputs  $I_7$  to  $I_4$  based on the values of selection lines  $s_1 \& s_0$ .

Therefore, the overall combination of two 4x1 Multiplexers and one 2x1 Multiplexer performs as one 8x1 Multiplexer.

# 16x1 Multiplexer

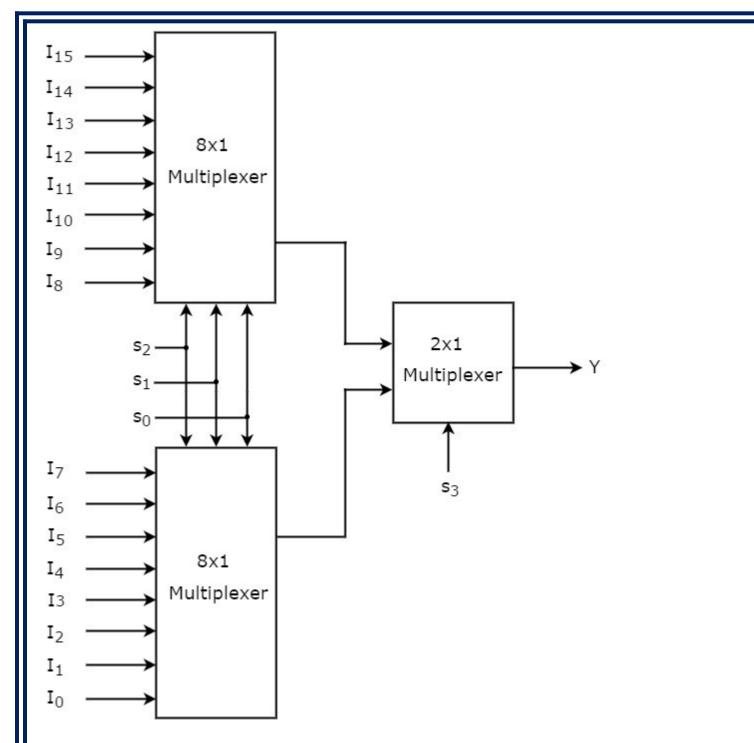

In this section, let us implement 16x1 Multiplexer using 8x1 Multiplexers and 2x1 Multiplexer. We know that 8x1 Multiplexer has 8 data inputs, 3 selection lines and one output. Whereas, 16x1 Multiplexer has 16 data inputs, 4 selection lines and one output.

So, we require two **8x1 Multiplexers** in first stage in order to get the 16 data inputs. Since, each 8x1 Multiplexer produces one output, we require a 2x1 Multiplexer in second stage by considering the outputs of first stage as inputs and to produce the final output.

Let the 16x1 Multiplexer has sixteen data inputs  $I_{15}$  to  $I_0$ , four selection lines  $s_3$  to  $s_0$  and one output Y. The **Truth table** of 16x1 Multiplexer is shown below.

|                | Output         |                |                |                  |

|----------------|----------------|----------------|----------------|------------------|

| S <sub>3</sub> | S <sub>2</sub> | S <sub>1</sub> | S <sub>0</sub> | Υ                |

| 0              | 0              | 0              | 0              | II <sub>0</sub>  |

| 0              | 0              | 0              | 1              | II <sub>1</sub>  |

| 0              | 0              | 1              | 0              | II <sub>2</sub>  |

| 0              | 0              | 1              | 1              | II <sub>3</sub>  |

| 0              | 1              | 0              | 0              | 114              |

| 0              | 1              | 0              | 1              | 115              |

| 0              | 1              | 1              | 0              | 116              |

| 0              | 1              | 1              | 1              | II <sub>7</sub>  |

| 1              | 0              | 0              | 0              | II <sub>8</sub>  |

| 1              | 0              | 0              | 1              | II <sub>9</sub>  |

| 1              | 0              | 1              | 0              | II <sub>10</sub> |

| 1              | 0              | 1              | 1              | II <sub>11</sub> |

| 1              | 1              | 0              | 0              | II <sub>12</sub> |

| 1              | 1              | 0              | 1              | II <sub>13</sub> |

| 1              | 1              | 1              | 0              | II <sub>14</sub> |

| 1              | 1              | 1              | 1              | II <sub>15</sub> |

We can implement 16x1 Multiplexer using lower order Multiplexers easily by considering the above Truth table. The **block diagram** of 16x1 Multiplexer is shown in the following figure.

The same selection lines,  $s_2$ ,  $s_1$  &  $s_0$  are applied to both 8x1 Multiplexers. The data inputs of upper 8x1 Multiplexer are  $I_{15}$  to  $I_{15}$  to  $I_{15}$  and the data inputs of lower 8x1 Multiplexer are  $I_{17}$  to  $I_{17}$ . Therefore, each 8x1 Multiplexer produces an output based on the values of selection lines,  $s_2$ ,  $s_1$  &  $s_2$ .

The outputs of first stage 8x1 Multiplexers are applied as inputs of 2x1 Multiplexer that is present in second stage. The other **selection line**, **s**₃ is applied to 2x1 Multiplexer.

- If  $s_3$  is zero, then the output of 2x1 Multiplexer will be one of the 8 inputs  $Is_7$  to  $I_0$  based on the values of selection lines  $s_2$ ,  $s_1$  &  $s_0$ .

- If  $s_3$  is one, then the output of 2x1 Multiplexer will be one of the 8 inputs  $I_{15}$  to  $I_8$  based on the values of selection lines  $s_2$ ,  $s_1$  &  $s_0$ .

Therefore, the overall combination of two 8x1 Multiplexers and one 2x1 Multiplexer performs as one 16x1 Multiplexer.

#### **De-Multiplexer**

is a combinational circuit that performs the reverse operation of Multiplexer. It has single input, 'n' selection lines and maximum of 2<sup>n</sup> outputs. The input will be connected to one of these outputs based on the values of selection lines.

Since there are 'n' selection lines, there will be 2<sup>n</sup> possible combinations of zeros and ones. So, each combination can select only one output. De-Multiplexer is also called as **De-Mux**.

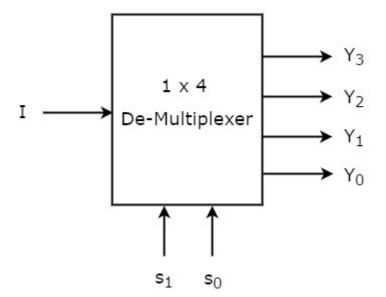

## 1x4 De-Multiplexer

1x4 De-Multiplexer has one input I, two selection lines,  $s_1$  &  $s_0$  and four outputs  $Y_3$ ,  $Y_2$ ,  $Y_1$  & $Y_0$ . The **block diagram** of 1x4 De-Multiplexer is shown in the following figure.

The single input 'l' will be connected to one of the four outputs,  $Y_3$  to  $Y_0$  based on the values of selection lines  $s_1$  & s0. The **Truth table** of 1x4 De-Multiplexer is shown below.

| Sellect | Outpu<br>ts |        |        |      |        |

|---------|-------------|--------|--------|------|--------|

| S       | S           | Υ      | Υ      | Υ    | Υ      |

| 1       | 0           | 3      | 2      | 1    | 0      |

| 0       | 0           | 0      | 0      | 0    | l<br>I |

| 0       | 1           | 0      | 0      | <br> | 0      |

| 1       | 0           | 0      | I<br>I | 0    | 0      |

| 1       | 1           | I<br>I | 0      | 0    | 0      |

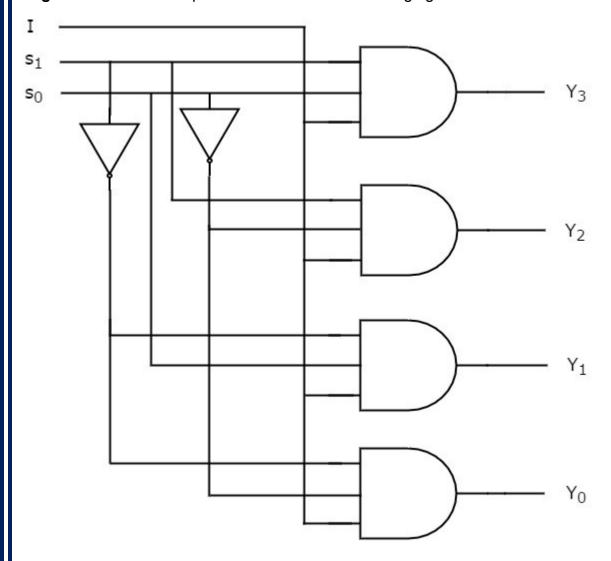

From the above Truth table, we can directly write the **Boolean functions** for each output as

$$Y_3=s_1s_0Iy_3=s_1s_0I$$

$$Y_2 = S_1S_0/I$$

Y2=s1s0'I

$$Y_1=s_1/s_0I$$

Y1=s1's0I

$$Y_0 = S_1 / S_0 / I Y_0 = S_1 / S_0 / I$$

We can implement these Boolean functions using Inverters & 3-input AND gates. The **circuit diagram** of 1x4 De-Multiplexer is shown in the following figure.

We can easily understand the operation of the above circuit. Similarly, you can implement 1x8 De-Multiplexer and 1x16 De-Multiplexer by following the same procedure.

## **Implementation of Higher-order De-Multiplexers**

Now, let us implement the following two higher-order De-Multiplexers using lower-order De-Multiplexers.

- 1x8 De-Multiplexer

- 1x16 De-Multiplexer

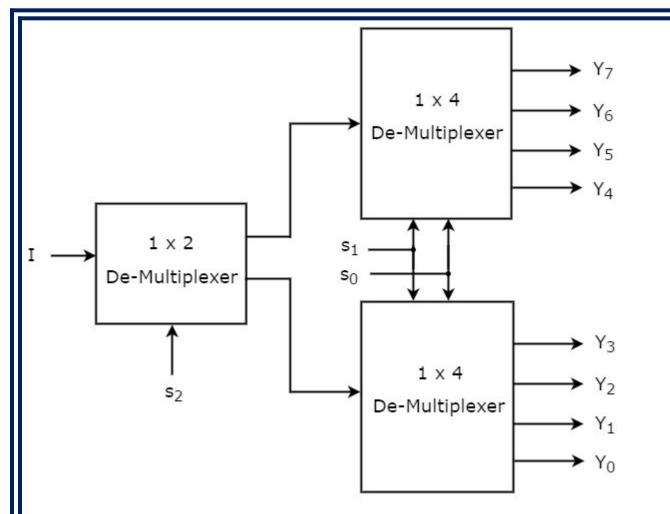

## <u>1x8 De-Multiplexer</u>

In this section, let us implement 1x8 De-Multiplexer using 1x4 De-Multiplexers and 1x2 De-Multiplexer. We know that 1x4 De-Multiplexer has single input, two selection lines and four outputs. Whereas, 1x8 De-Multiplexer has single input, three selection lines and eight outputs.

So, we require two **1x4 De-Multiplexers** in second stage in order to get the final eight outputs. Since, the number of inputs in second stage is two, we require **1x2 DeMultiplexer** in first stage so

that the outputs of first stage will be the inputs of second stage. Input of this 1x2 De-Multiplexer will be the overall input of 1x8 De-Multiplexer.

Let the 1x8 De-Multiplexer has one input I, three selection lines  $s_2$ ,  $s_1$  &  $s_0$  and outputs  $Y_7$  to  $Y_0$ . The **Truth table** of 1x8 De-Multiplexer is shown below.

| Sellectiion IInputs |                |                | Outpu<br>ts |                       |                       |                       |          |        |          |          |

|---------------------|----------------|----------------|-------------|-----------------------|-----------------------|-----------------------|----------|--------|----------|----------|

| <b>S</b>            | S <sub>1</sub> | S <sub>0</sub> | <b>Y</b> 7  | <b>Y</b> <sub>6</sub> | <b>Y</b> <sub>5</sub> | <b>Y</b> <sub>4</sub> | <b>Y</b> | Y<br>2 | <b>Y</b> | <b>Y</b> |

| 0                   | 0              | 0              | 0           | 0                     | 0                     | 0                     | 0        | 0      | 0        | l<br>I   |

| 0                   | 0              | 1              | 0           | 0                     | 0                     | 0                     | 0        | 0      | I<br>I   | 0        |

| 0                   | 1              | 0              | 0           | 0                     | 0                     | 0                     | 0        | I<br>I | 0        | 0        |

| 0                   | 1              | 1              | 0           | 0                     | 0                     | 0                     | I<br>I   | 0      | 0        | 0        |

| 1                   | 0              | 0              | 0           | 0                     | 0                     | II                    | 0        | 0      | 0        | 0        |

| 1                   | 0              | 1              | 0           | 0                     | II                    | 0                     | 0        | 0      | 0        | 0        |

| 1                   | 1              | 0              | 0           | II                    | 0                     | 0                     | 0        | 0      | 0        | 0        |

| 1                   | 1              | 1              | I           | 0                     | 0                     | 0                     | 0        | 0      | 0        | 0        |

We can implement 1x8 De-Multiplexer using lower order Multiplexers easily by considering the above Truth table. The **block diagram** of 1x8 De-Multiplexer is shown in the following figure.

The common **selection lines**,  $s_1$  &  $s_0$  are applied to both 1x4 De-Multiplexers. The outputs of upper 1x4 De-Multiplexer are  $Y_7$  to  $Y_4$  and the outputs of lower 1x4 De-Multiplexer are  $Y_3$  to  $Y_0$ .

The other **selection line**,  $s_2$  is applied to 1x2 De-Multiplexer. If  $s_2$  is zero, then one of the four outputs of lower 1x4 De-Multiplexer will be equal to input, I based on the values of selection lines  $s_1$  &  $s_0$ . Similarly, if  $s_2$  is one, then one of the four outputs of upper 1x4 DeMultiplexer will be equal to input, I based on the values of selection lines  $s_1$  &  $s_0$ .

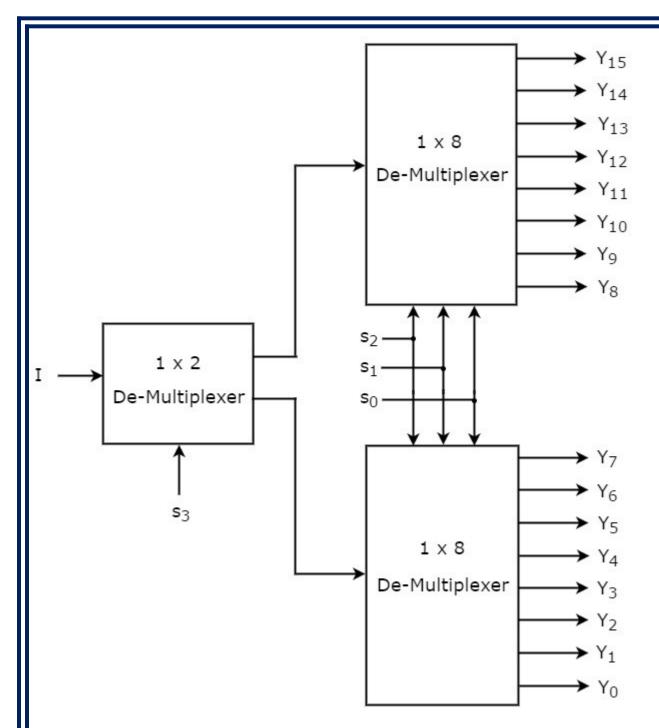

# 1x16 De-Multiplexer

In this section, let us implement 1x16 De-Multiplexer using 1x8 De-Multiplexers and 1x2 De-Multiplexer. We know that 1x8 De-Multiplexer has single input, three selection lines and eight outputs. Whereas, 1x16 De-Multiplexer has single input, four selection lines and sixteen outputs.

So, we require two **1x8 De-Multiplexers** in second stage in order to get the final sixteen outputs. Since, the number of inputs in second stage is two, we require **1x2 DeMultiplexer** in first stage so that the outputs of first stage will be the inputs of second stage. Input of this 1x2 De-Multiplexer will be the overall input of 1x16 De-Multiplexer.

Let the 1x16 De-Multiplexer has one input I, four selection lines  $s_3$ ,  $s_2$ ,  $s_1$  &  $s_0$  and outputs  $Y_{15}$  to  $Y_0$ . The **block diagram** of 1x16 De-Multiplexer using lower order Multiplexers is shown in the following figure.

The common **selection lines s<sub>2</sub>, s<sub>1</sub> & s<sub>0</sub>** are applied to both 1x8 De-Multiplexers. The outputs of upper 1x8 De-Multiplexer are  $Y_{15}$  to  $Y_{15}$  and the outputs of lower 1x8 DeMultiplexer are  $Y_{7}$  to  $Y_{15}$ .

The other **selection line**,  $s_3$  is applied to 1x2 De-Multiplexer. If  $s_3$  is zero, then one of the eight outputs of lower 1x8 De-Multiplexer will be equal to input, I based on the values of selection lines  $s_2$ ,  $s_1$  &  $s_0$ . Similarly, if  $s_1$  is one, then one of the 8 outputs of upper 1x8 De-Multiplexer will be equal to input, I based on the values of selection lines  $s_2$ ,  $s_1$  &  $s_0$ .