# بسم الله الرحمن الرحيم

## جامعة الموصل – كلية علوم الحاسوب والرياضيات قسم الامن السيبراني

#### **CIRCUTE DESIGN**

المحاضرة الأولى Logic Gates

Sura Sabah I. Ahmed

#### **Logic Gates**

There are a basic elements that makeup a digital system.

The electronic gates: It is a circuit that is able to operate on a number of binary inputs in order to perform a particular logical function. The GATE is used to describe a circuit that performs a basic logic operation.

According to the type of logical operation between inputs and output basically there are 8 standard gates which are used in digital circuit design.

They are: AND, OR, NOT, NAND, NOR, EXCLUSIVE-OR, EXCLUSIVE NOR, and TRANSFER (BUFFER).

It is one of the basic gates which has two or more inputs and one output. It performs what is known as LOGICAL MULTIPLICATION.

#### Two inputs AND Gate

If two inputs A and B are combined using the AND operation, the result can be represented as Y=A.B or Y=AB. In this expression the "dot" sign standard for Boolean AND operation.

The Logic symbol of Two inputs AND Gate is:

The output equation or output expression:

- ➤ The operation of AND Gate is such that the output is HIGH only when all of the inputs are HIGH.

- When any of the input is LOW, the output is LOW.

The truth table of two inputs AND gate:

| A | В | Y=A.B |  |  |

|---|---|-------|--|--|

| 0 | 0 | 0     |  |  |

| 0 | 1 | 0     |  |  |

| 1 | 0 | 0     |  |  |

| 1 | 1 | 1     |  |  |

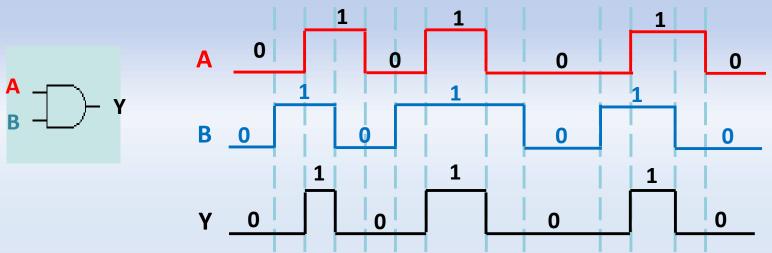

#### Pulsed Operation:

In many application, the input to a gate may be voltages that change with time between the two logic levels and are called as pulsed waveform. In studying the pulsed operation of the AND gate, we consider the inputs with respect to each other in order to determine the output level at any given time.

High (1)

The Logic levels:

Low (0)

#### Example:

Determine the output y from the AND gate for the given input waveforms shown below.

#### Standard Package:

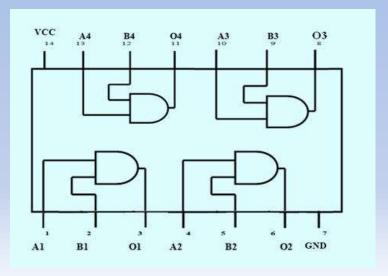

The pin diagram of the chip (IC 7408), a TTL quad-2 input AND gate is shown below, this IC contains (Four 2-input AND gate) and it is (14-pin dual-line package).

The TTL quad-2 input AND gate (7408)

The pin diagram of the chip (IC 7408)

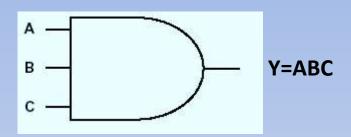

#### Three inputs AND gate:

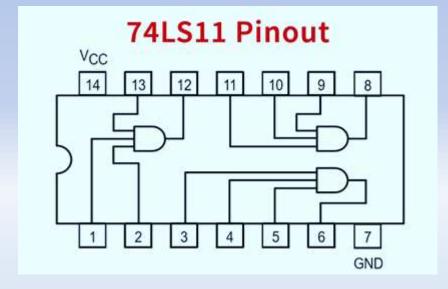

The pin diagram of the chip (IC 7411)

## The truth table of three inputs AND gate:

| INPUTS |   |   | OUTPUT |

|--------|---|---|--------|

| Α      | В | С | Y=ABC  |

| 0      | 0 | 0 | 0      |

| 0      | 0 | 1 | 0      |

| 0      | 1 | 0 | 0      |

| 0      | 1 | 1 | 0      |

| 1      | 0 | 0 | 0      |

| 1      | 0 | 1 | 0      |

| 1      | 1 | 0 | 0      |

| 1      | 1 | 1 | 1      |

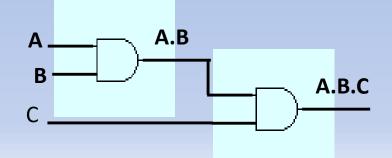

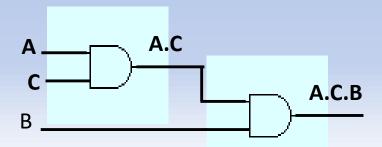

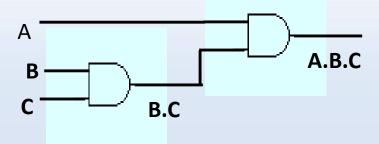

Build a 3-inputs AND gates using TWO 2-nputs AND gates only?

We can use two (2-inputs AND gates) to perform three inputs AND operation.

Since A.B=B.A then The output equation can be written as : Y=A.B.C. Y=(A.B).C or Y=A.(B.C) or Y=(A.C).B

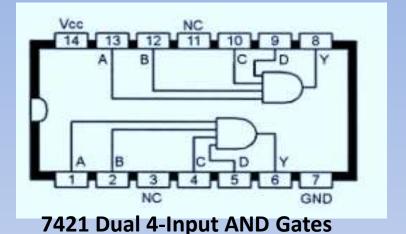

#### Four inputs AND gate:

H.W:

Write the truth table and the output equation of the 4-inputsn AND gate?

#### **Conclusion:**

- 1) The AND operation is performed like ordinary multiplication of 1's and 0's.

- 2) An output equal to "1" occurs only for the single case where all inputs are "1".

- 3) The output is "0" for any case where one or more inputs are "0".

- 4) For an n-inputs AND gate, the output Y=A.B.C.........

- 5) With AND operation 1.1=1, 1.1.1.1. so on=1.

#### Application Example:

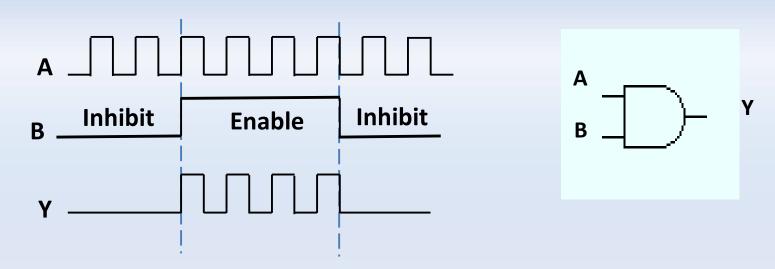

#### The AND date as Enable/Inhibit Device:

- A common application of the AND gate is to enable (that is to allow) the passage of a signal (pulse waveform) from one point to another at certain times and to inhibit (prevent) the passage at another times.

- A simple example of this particular use of an AND gate is shown below, where the AND gate controls the passage of a signal (waveform A). The enable pulse is applied at A input. When the enable pulse is HIGH, waveform passes through the date, and when the enable pulse is LOW, waveform A is prevented from passing through the gate, that is inhibited (or the gate is disabled).

### Thank you