# Logical Design Lecture 13

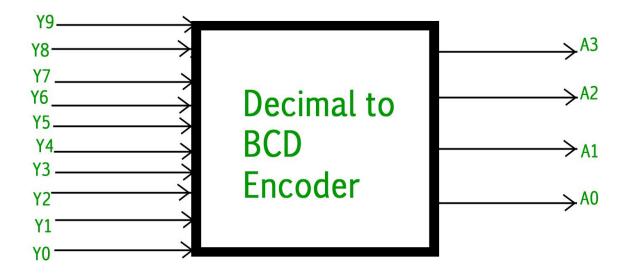

#### **Decimal to BCD Encoder**

#### Homework:

Design a decimal to binary encoder. The decimal to binary encoder consists of **10 input lines** and **4 output lines**. Each input line corresponds to each decimal digit and 4 outputs correspond to the BCD code. This encoder accepts the decoded decimal data as an input and encodes it to the BCD output which is available on the output lines.

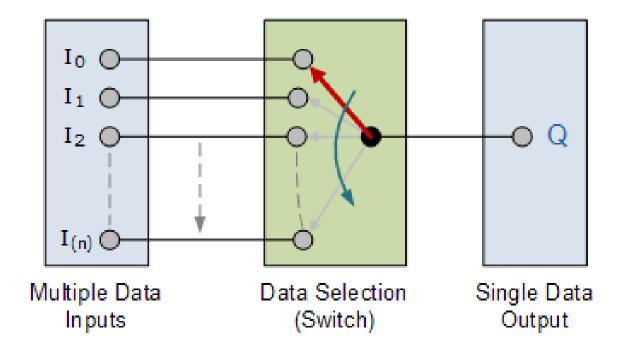

## Multiplexers (MUX)

The **multiplexer** is a combinational logic circuit designed to switch one of several input lines to a single common output line

- Reduce the number of wires

- Reduce circuit complexity and cost

- The multiplexer is a very useful electronic circuit that has uses in many different applications such as signal routing, data communications and data bus control applications.

#### Multiplexers

**multiplexers** are also known as data selectors because they can "select" each input line.

Generally, the selection of each input line in a multiplexer is controlled by an additional set of inputs called *control lines* and according to the binary condition of these control inputs, either "HIGH" or "LOW" the appropriate data input is connected directly to the output.

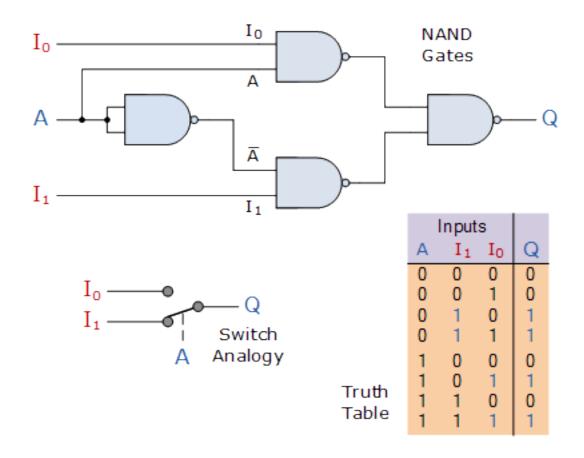

### 2-input Multiplexer Design

The input A of this simple 2-1 line multiplexer circuit constructed from standard NAND gates acts to control which input ( $I_0$  or  $I_1$ ) gets passed to the output at Q.

From the truth table, we can see that when the data select input, A is LOW at logic 0, input  $I_1$  passes its data through the NAND gate multiplexer circuit to the output, while input  $I_0$  is blocked. When the data select A is HIGH at logic 1, the reverse happens and now input  $I_0$  passes data to the output Q while input  $I_1$  is blocked.

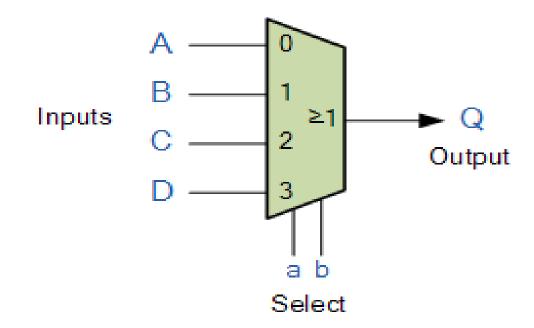

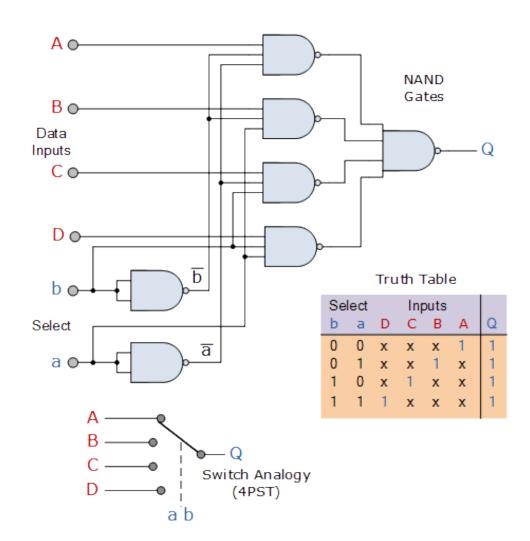

#### 4-to-1 Channel Multiplexer

Larger multiplexer circuits can be created using smaller 2-to-1 multiplexers as their basic building blocks, and the number of data inputs can be increased simply by following the same approach.

The Boolean expression for this 4-to-1 **Multiplexer** above with inputs A to D and data select lines a, b is given as:

$$Q = \overline{ab}A + a\overline{b}B + \overline{a}bC + abD$$

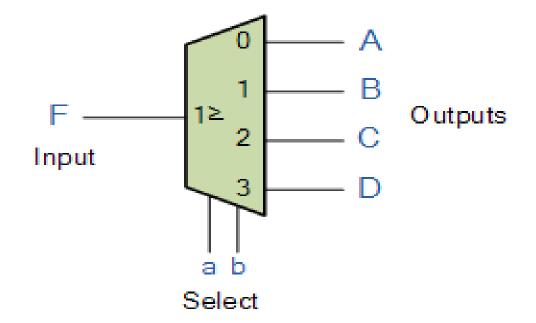

### Demultiplexers (Demux)

The *demultiplexer* is a combinational logic circuit designed to switch one common input line to one of several separate output line.

The *demultiplexer* takes one single input data line and then switches it to any one of a number of individual output lines one at a time. The **demultiplexer** converts a serial data signal at the input to a parallel data at its output lines as shown in the figure.