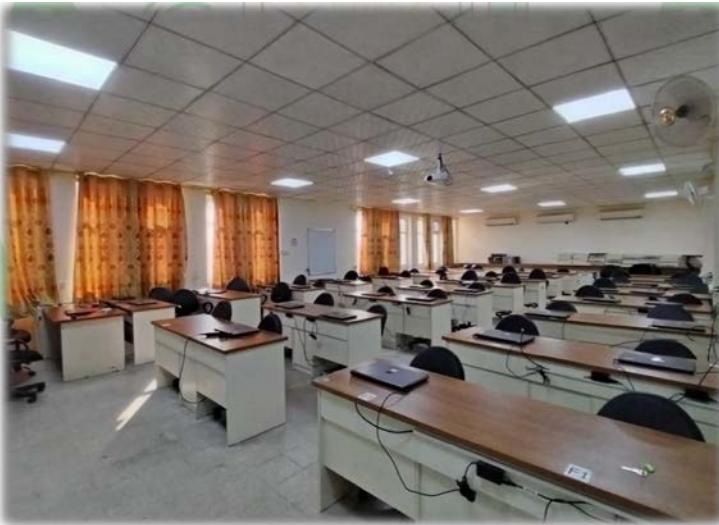

جامعة الموصل / كلية الهندسة /

قسم هندسة الحاسوب

مختبرات المستوى الثاني

## وصف مختبر المعالجات الدقيقة I

### 1. المعلومات العامة:

|                                |                                       |

|--------------------------------|---------------------------------------|

| اسم المختبر و رقم المختبر:     | مختبر المعالجات الدقيقة I (مختبر 312) |

| اسم المقرر المرتبط:            | المعالجات الدقيقة I                   |

| القسم:                         | هندسة الحاسوب                         |

| عدد الساعات الأسبوعية للمختبر: | 3 ساعات                               |

| عدد أسابيع الفصل الدراسي:      | 15 أسبوعاً                            |

| المستوى الدراسي:               | المستوى الثاني                        |

| المشرف على المختبر:            | د. مازن هاشم عزيز                     |

### 2. وصف عام للمختبر:

يهدف مختبر المعالجات الدقيقة I إلى تعزيز المفاهيم النظرية التي تم تناولها في محاضرات مقرر المعالجات الدقيقة I ، من خلال تطبيقات عملية واقعية باستخدام أدوات وبرمجيات مخصصة للمعالجات الدقيقة، يوفر المختبر بيئة تفاعلية تمكن الطالب من اكتساب مهارات كتابة البرمجيات بلغة التجميع وتنفيذها وتتبع الأخطاء واكتشافها وتصحيحها.

### 3. أهداف المختبر:

- تدريب الطالب على كتابة البرمجيات بلغة التجميع.

- التعرف على الإياعزات المختلفة.

- التدرب على استخدام الأدوات البرمجية.

- استخدام بيئة المحاكاة في تتبع وكشف الأخطاء وتصحيحها.

- كتابة تطبيقات متدرجة التعقيد وعرض النتائج وتحسينها.

- تعزيز القدرة على تنفيذ المشاريع.

#### 4. مخرجات التعلم:

بنهاية المختبر، يجب أن يكون الطالب قادرًا على:

- كتابة برامج بلغة التجميع.

- تتبع وكشف الأخطاء وتصحيفها.

- تنفيذ البرامج بلغة التجميع.

- كتابة وتنفيذ تطبيقات برمجية متوسطة المستوى بلغة التجميع.

- إكتساب روح العمل الفرقي.

#### 5. الجدول الأسبوعي للتجارب:

| الأسبوع | عنوان التجربة                  | الأدوات / البرامج المستخدمة | الهدف الرئيسي                                            |

|---------|--------------------------------|-----------------------------|----------------------------------------------------------|

| 1       | مقدمة عن الأدوات المستخدمة     | حاسوب                       | التعرف على مفاهيم استخدام لغة التجميع                    |

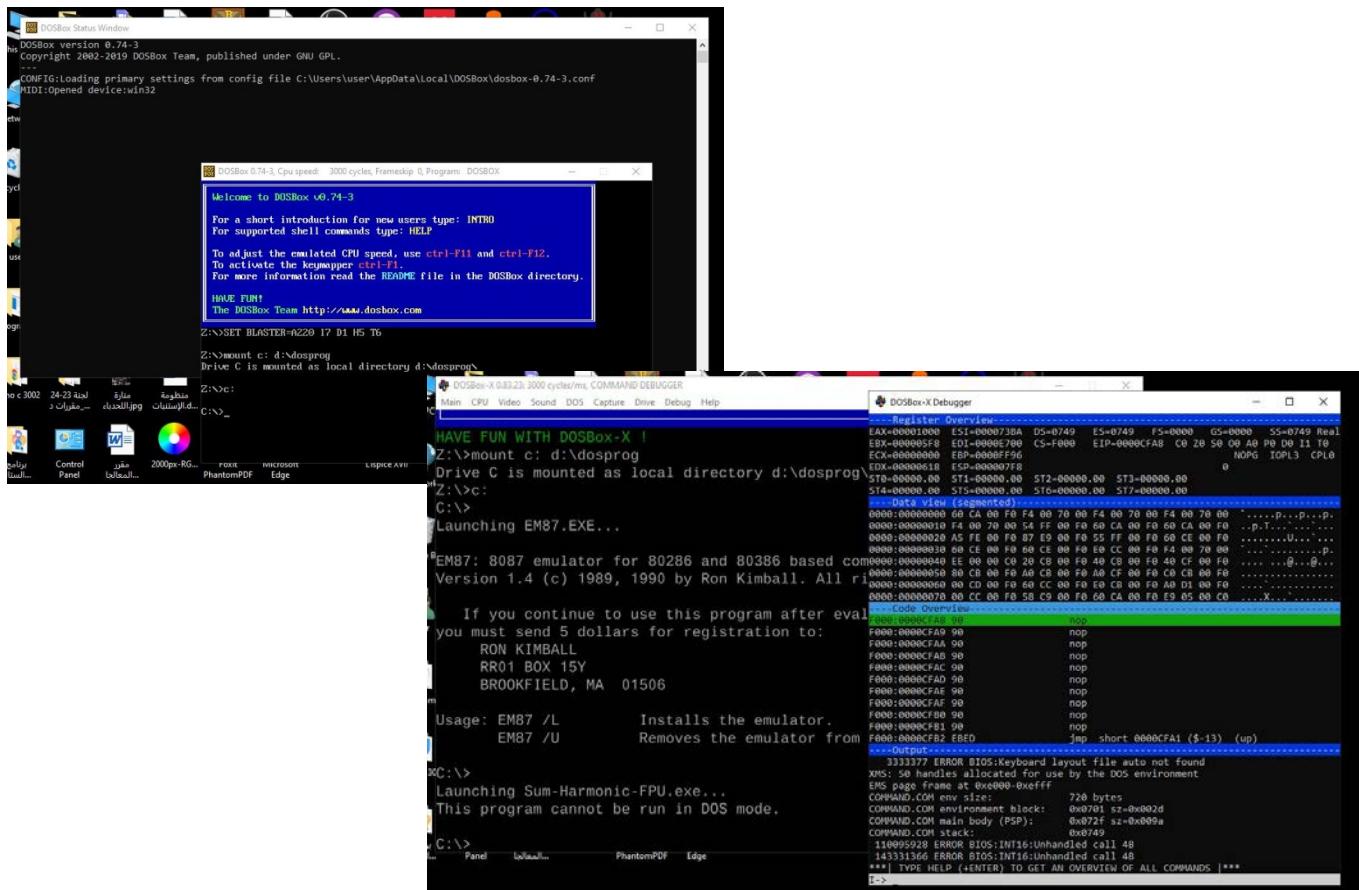

| 2       | إعداد بيئة DOSBOX              | DOSBOX                      | استخدام بيئة افتراضية                                    |

| 3       | إعداد برنامج Debug             | تنصيب برنامج Debug          | تعلم استخدام البرنامج لكشف وتتبع الأخطاء وتصحيفها        |

| 4       | إعداد برنامج Masm & Link       | تنصيب برامج Masm & Link     | التعرف على كيفية الكتابة بلغة التجميع وصولاً إلى التنفيذ |

| 5       | كتابة برنامج بسيط بلغة التجميع | محرر نصوص + البرمجيات       | تطبيق مبسط                                               |

| 6       | إياعازات نقل البيانات          | محرر نصوص + البرمجيات       | استخدام إياعازات نقل البيانات                            |

| 7       | إياعازات المنطقية              | محرر نصوص + البرمجيات       | استخدام الإياعازات المنطقية                              |

| 8       | إياعازات التزحيف واتدوير       | محرر نصوص + البرمجيات       | استخدام إياعازات التزحيف واتدوير                         |

| 9       | إياعازات التفريع               | محرر نصوص + البرمجيات       | استخدام إياعازات التفريع                                 |

| 10      | إياعازات الحسابية              | محرر نصوص + البرمجيات       | استخدام الإياعازات الحسابية                              |

| 11      | إياعازات السلسلة               | محرر نصوص + البرمجيات       | استخدام إياعازات السلسلة                                 |

|                                        |                       |                                 |    |

|----------------------------------------|-----------------------|---------------------------------|----|

| استخدام إيعازات السيطرة                | محرر نصوص + البرمجيات | إيعازات السيطرة                 | 12 |

| تطبيق تفاعلي من خلال الذاكرة الفيديوية | محرر نصوص + البرمجيات | التعامل مع الذاكرة الفيديوية    | 13 |

| دمج المهارات المكتسبة في مشروع نهائي   | محرر نصوص + البرمجيات | تطبيقات باستخدام برامج المقاطعة | 14 |

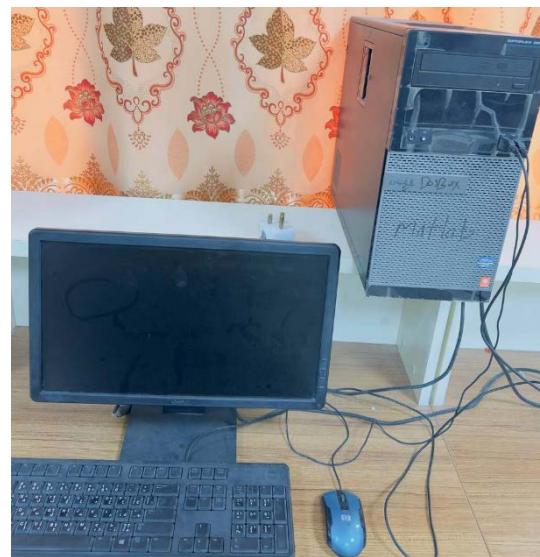

#### 6. الأدوات والمعدات المستخدمة:

- حواسيب.

- برمجيات.

#### 7. دليل السلامة:

- التأكد من فصل التيار الكهربائي عند توصيل الأجهزة.

- عدم لمس المنافذ الكهربائية أو مكونات الشبكة دون إذن المشرف.

- الالتزام بالهدوء وتنظيم الكابلات لتجنب الحوادث.

- استخدام البرنامج المحاكي لتجارب التوجيه قبل التجربة على الأجهزة الحقيقية.

#### 8. آلية التقييم:

| عنصر التقييم             | النسبة |

|--------------------------|--------|

| الحضور والمشاركة         | 10%    |

| تقارير التجارب الأسبوعية | 30%    |

| الاختبارات القصيرة       | 20%    |

| الامتحان العملي النهائي  | 30%    |

| المشروع العملي           | 10%    |

## 9. المراجع والمصادر:

- Walter Triebel and Avtar Singh, The 8088 and 8086 Microprocessors: programming, Interfacing, software, Hardware, Applications, 4th edition, prentice-Hall, 2002.

- Lectures, experiment manual, and notes

- The Intel microprocessors 8086/8088, 80186/80188, 80286, 80386, 80486, Pentium, Pentium Pro processor, Pentium II, Pentium III, Pentium 4, and Core2 with 64-bit extensions: architecture, programming, and interfacing by: Barry B. Brey—8th ed.

- <https://classroom.google.com/c/NzEyMjE0ODcyMTUx>

- [https://www.eng.auburn.edu/~sylee/ee2220/8086\\_instruction\\_set.html](https://www.eng.auburn.edu/~sylee/ee2220/8086_instruction_set.html)

## 10. المرفقات:

- نموذج تقرير التجربة

## Data Transfer Instructions

### Objective:-

- Learn how to use data transfer instructions.

### Equipments:-

- PC

### Procedure:-

For the steps (1, 4) write the instructions using (A) command, then execute them step by step using (T) command.

1. Use (D) command after each step from (h-k) to observe the contents of the specified memory locations:

- R

- A 100

- XXXX:0100 MOV CX,1122 CX=... ..

- XXXX:0103 MOV AX,3344 AX=... ..

- XXXX:0106 XCHG CL,AH AX=... .. ,CX=... ..

- XXXX:0108 MOV BX,10 BX=... ..

- XXXX:010B MOV DI,200 DI=... ..

- XXXX:010E MOV DX,5566 DX=... ..

- i)XXXX:0111 MOV AL,[BX] AL=.....

- j)XXXX:0113 LEA SI,[BX] SI=.....

- k) XXXX:0115 LDS DI,[BX] DI=..... ,DS=.....

- l)XXXX:0117 LES BX,[DI] BX=..... ,ES=.....

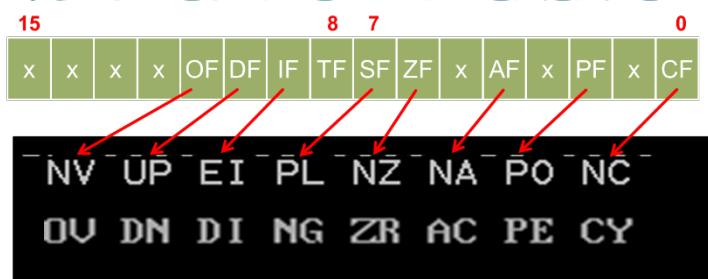

### FLAG REGISTER TO REMEMBER

2. Apply each of the following steps (a through g), then state the results.

- RF

- RAX AH=... .. ..

- A 100

- XXXX:0100 LAHF <ENTER>

- T=100

- RAX AH=... .. ..

- RF

Apply each of the following steps (a through f), then state the results.

- a) -A 100

- b) XXXX:0100 MOV AH,0

- c) XXXX:01XX SAHF <ENTER>

- d) -T=100

- e) -RAX

- f) -RF Flag register=.....

3. Apply each of the following steps (a through o), then use (D) command prior to each XLAT instruction to observe the contents of the specified memory locations:

- a) -R

- b) -F 100 120 "MICROPROCESSOR LAB"

- c) -F 200 220 "microprocessor lab"

- d) -A 100

- e) XXXX:0100 MOV AL,0 AL=...

- f) XXXX:01XX MOV BX,100 BX=...

- g) XXXX:01XX MOV DI,200 DI=...

- h) XXXX:01XX XLAT AL=...

- i) XXXX:01XX MOV AL,9 AL=...

- j) XXXX:01XX XLAT AL=...

- k) XXXX:01XX XCHG DI,BX DI=...,BX=...

- l) XXXX:01XX MOV AL,9 AL=...

- m) XXXX:01XX XLAT AL=...

- n) XXXX:01XX MOV AL,F AL=...

- o) XXXX:01XX XLAT AL=...

## وصف مختبر المعالجات الدقيقة 2

### 1. المعلومات العامة:

|                                |                                        |

|--------------------------------|----------------------------------------|

| اسم المختبر و رقم المختبر:     | مختبر المعالجات الدقيقة II (مختبر 312) |

| اسم المقرر المرتبط:            | المعالجات الدقيقة II                   |

| القسم:                         | هندسة الحاسوب                          |

| عدد الساعات الأسبوعية للمختبر: | 3 ساعات                                |

| عدد أسابيع الفصل الدراسي:      | 15 أسبوعاً                             |

| المستوى الدراسي:               | المستوى الثاني                         |

| المشرف على المختبر:            | د. مازن هاشم عزيز                      |

### 2. وصف عام للمختبر:

يهدف مختبر المعالجات الدقيقة II إلى تعزيز المفاهيم النظرية التي تم تناولها في محاضرات مقرر المعالجات الدقيقة II ، من خلال تطبيقات عملية واقعية باستخدام أدوات وبرمجيات مخصصة للمعالجات الدقيقة، يوفر المختبر بيئة تفاعلية تُمكّن الطالب من اكتساب مهارات تصميم دوائر الموازنة مع المعالج الدقيق 8086 وكتابة البرمجيات بلغة التجميع وتنفيذها في بيئة افتراضية وعرض المخططات الزمنية وتحليل النتائج.

### 3. أهداف المختبر:

- تدريب الطلاب على التصميم.

- التعرف على العناصر الرقمية المختلفة.

- التدرب على استخدام الأدوات الإفتراضية.

- استخدام بيئة المحاكاة في إعداد التصاميم والتعديل عليها.

- كتابة البرمجيات بلغة التجميع وتنفيذها باستخدام التصاميم المعدة وعرض النتائج وتحسينها.

- تعزيز القدرة على تنفيذ المشاريع.

#### 4. مخرجات التعلم:

بنهاية المختبر، يجب أن يكون الطالب قادرًا على:

- استخدام بيئة المحاكاة Proteus.

- إعداد التصاميم وتنفيذها.

- تنفيذ البرامج بلغة التجميع وتطبيقها على التصاميم المعدة.

- تحليل النتائج وإيجاد الأخطاء وتحسين التصاميم.

- إكتساب روح العمل الفرقي.

#### 5. الجدول الأسبوعي للتجارب:

| الأسبوع | عنوان التجربة                                                           | الأدوات / البرامج المستخدمة | الهدف الرئيسي                                                                                                |

|---------|-------------------------------------------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------|

| 1       | مقدمة عن الأدوات المستخدمة                                              | حاسوب                       | التعرف على مفاهيم استخدام أدوات المحاكاة في التصاميم                                                         |

| 2       | إعداد بيئة Proteus                                                      | تنصيب بيئة Proteus          | إكتساب مهارة تنصيب البرمجيات وإعدادها                                                                        |

| 3       | أدوات التصميم والمكتبات المتوفرة                                        | Proteus                     | التعرف على الأدوات التي يوفرها Proteus وكيفية توظيفها                                                        |

| 4       | تصميم وتنفيذ لمحاكاة دوائر منطقية بسيطة                                 | Proteus                     | استخدام أدوات التصميم في تنفيذ دوائر منطقية بسيطة والتعرف على أدوات محاكاة إشارات الإدخال وأدوات عرض النتائج |

| 5       | تصميم وتنفيذ دائرة لمحاكاة المعالج الدقيق 8086 منفرداً                  | Proteus                     | تنفيذ دائرة معالج دقيق وكتابة أول برنامج له لعرض إشارات المعالج                                              |

| 6       | تصميم وتنفيذ دائرة لمحاكاة نوافل العناوين والبيانات للمعالج الدقيق 8086 | Proteus                     | تطبيق المعرفة النظرية في التعرف على نوافل المعالج                                                            |

| 7       | تصميم وتنفيذ دائرة لمحاكاة فصل إشارات العناوين للمعالج الدقيق 8086      | Proteus                     | تطبيق المعرفة النظرية في فصل إشارات العناوين                                                                 |

| 8       | تصميم وتنفيذ دائرة لمحاكاة مصدات نوافل البيانات للمعالج الدقيق 8086     | Proteus                     | تطبيق المعرفة النظرية في بناء مصدات إشارات البيانات                                                          |

|                                                                                             |         |                                                                                    |    |

|---------------------------------------------------------------------------------------------|---------|------------------------------------------------------------------------------------|----|

| تطبيق المعرفة النظرية في بناء دائرة فك التشفير                                              | Proteus | تصميم وتنفيذ دائرة لمحاكاة فك تشفير العناوين للمعالج الدقيق 8086                   | 9  |

| تطبيق المعرفة النظرية في بناء دائرة مواءمة مع ذاكرة بحجم معين                               | Proteus | تصميم وتنفيذ دائرة لمحاكاة مواءمة المعالج الدقيق 8086 مع الذاكريات-1               | 10 |

| تطبيق المعرفة النظرية في تعديل دائرة المواءمة مع الذاكرة عند تغيير حجم الذاكرة              | Proteus | تصميم وتنفيذ دائرة لمحاكاة مواءمة المعالج الدقيق 8086 مع الذاكريات-2               | 11 |

| تطبيق المعرفة النظرية في بناء دائرة مواءمة مع طرفيات الإدخال والإخراج                       | Proteus | تصميم وتنفيذ دائرة لمحاكاة مواءمة المعالج الدقيق 8086 مع الطرفيات-1                | 12 |

| تطبيق المعرفة النظرية في بناء دائرة مواءمة مع طرفيات الإدخال والإخراج عند زيادة سعة كل منها | Proteus | تصميم وتنفيذ دائرة لمحاكاة مواءمة المعالج الدقيق 8086 مع الطرفيات-2                | 13 |

| دمج المهارات المكتسبة في مشروع نهائي                                                        | Proteus | تصميم وتنفيذ دائرة لمحاكاة مواءمة المعالج الدقيق 8086 مع الذاكريات والطرفيات سويةً | 14 |

#### 6. الأدوات والمعدات المستخدمة:

- حواسيب.

- طقم برمجيات المحاكاة Proteus.

#### 7. دليل السلامة:

- التأكد من فصل التيار الكهربائي عند توصيل الأجهزة.

- عدم لمس المنافذ الكهربائية أو مكونات الشبكة دون إذن المشرف.

- الالتزام بالهدوء وتنظيم الكابلات لتجنب الحوادث.

- استخدام البرنامج المحاكي لتجارب التوجيه قبل التجربة على الأجهزة الحقيقة.

#### 8. آلية التقييم:

| عنصر التقييم             | النسبة |

|--------------------------|--------|

| الحضور والمشاركة         | 10%    |

| تقارير التجارب الأسبوعية | 30%    |

| الاختبارات القصيرة       | 20%    |

| الامتحان العملي النهائي  | 30%    |

| المشروع العملي           | 10%    |

#### 9. المراجع والمصادر:

- The Intel microprocessors 8086/8088, 80186/80188, 80286, 80386, 80486, Pentium, Pentium Pro processor, Pentium II, Pentium III, Pentium 4, and Core2 with 64-bit extensions: architecture, programming, and interfacing by: Barry B. Brey—8th ed.

- <https://classroom.google.com/c/NzQ1Nzk2ODA2NjYx>

#### 10. المرفقات:

- نموذج تقرير التجربة

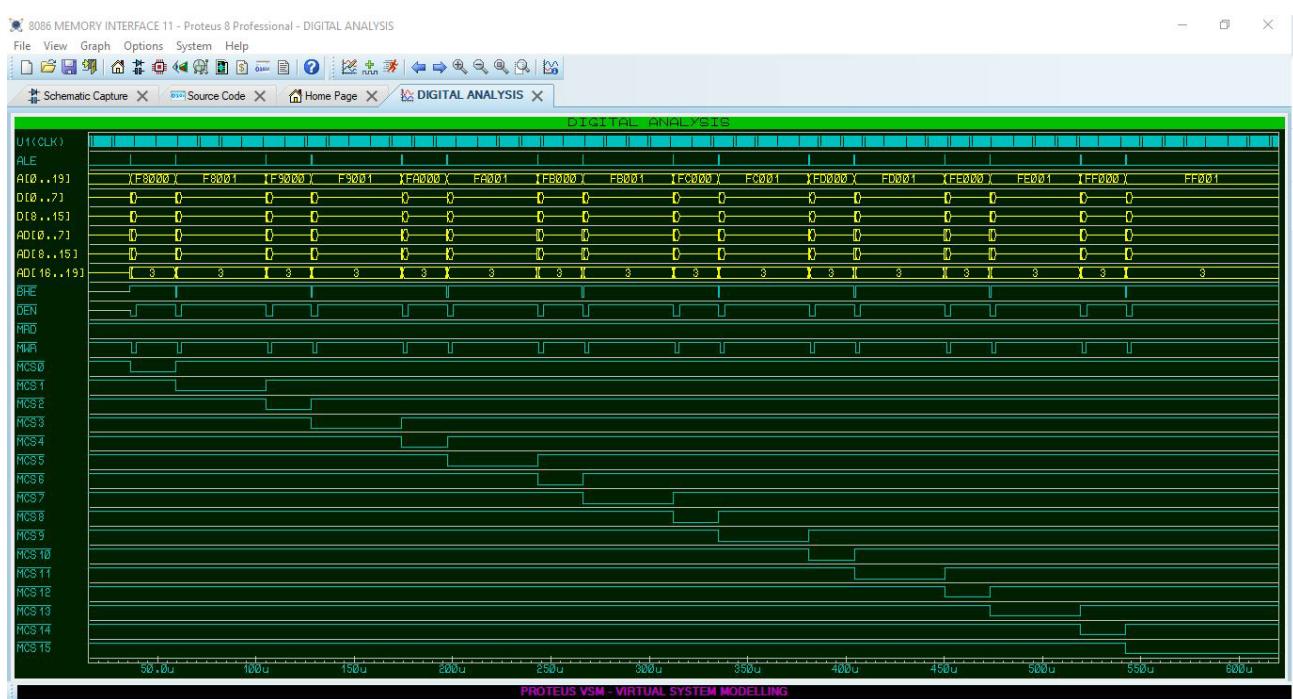

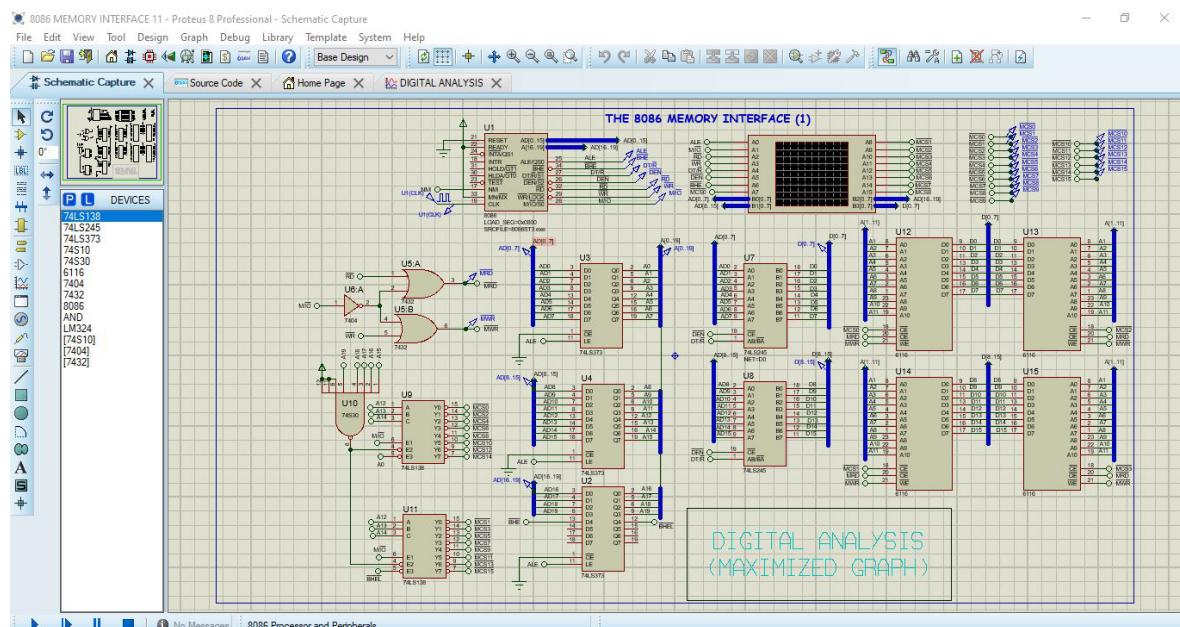

# **THE MEMORY INTERFACE (1)**

## **Chip Selects Generation**

---

### **Objective:-**

- Learning how to simulate an 8086-microprocessor using **Proteus8.1 suit** and perform memory chip select generation.

- Observing the effects of software changes on the outputs of the chips selection signals.

### **equipment:-**

- PC with **Proteus 8.1 Professional Design Suite** package.

### **Procedure:-**

- 1) Open the Proteus program as **administrator**.

- 2) Start a new project and name it (**8086 MEMORY INTERFACE 1++.pdsprj**).

- 3) Design the 8086 Microprocessor memory interface circuit as shown in (Fig. 1).

**(Hint. You can start from the previous experiment design.)**

- 4) The 8086- assembly program should have the following commands:

**HINT:** Assume the used memory chips are 2Kbytes each.

```

CODE SEGMENT PUBLIC 'CODE'

ASSUME CS: CODE

```

START:

1. CONT:

2. MOV AX,0F800h ;Segment Base Address

3. MOV DS, AX

4. MOV SI,0 ;Byte Pointer

5. MOV BX,0 ;Memory Chip Pointer

6. NXT:

7. MOV DL,0AAh ;Data for Even Byte

8. MOV [SI+BX], DL

9. MOV DL,0BBh ;Data for Odd Byte

10. MOV [SI+BX+1], DL

11. ADD BX,1000h ;Chip Pointer Increment (2X2Kbyte)

12. JMP NXT

```

CODE ENDS

```

```

END START

```

- 5) Start the simulation:

- (A) Either from the "Main-Menu-Bar", click on "Debug", then "Run Simulation", Or from the MDI control bar  at the left button of the screen.

- (B) If there were no errors, the simulation will start and a colored small square will flash near each pin of the working chips of the circuit, which indicate the state of each pin.

- 6) Right click on the Virtual Logic Analyzer, then go-down to the bottom of the menu and click on "VSM Logic Analyzer". The VSM Logic Analyzer window will be opened.

- 7) Ensure that the "Capture Resolution" knob setting is around 25ns, if not you can control the knob to get the required setting.

- 8) Click-on the "Capture " push-button and wait for the signals to be displayed.

- 9) Now the "Display Scale" knob can be used to control the display range for better observations.

- 10) Note that the signals will be displayed according to its connection sequence to the VSM Logic Analyzer in the circuit diagram.

- 11) You can watch the signals (ALE, RD, WR, BHE, DT/R, DEN, M/IO, AD0-19, MSC0, MCS1, .....).

- 12) Add a Digital Analysis Graph and add a Voltage Probe to monitor the above signals and buses.

### **Lab work:**

- (1) Add the digital analysis graph and add all buses and signals to it using the voltage probes and use it to watch the signals.

- (2) Add and connect the necessary signals to the logic analyzer and to the digital analysis graph and write the above code in the source code tab.

- (3) Run the simulator and draw the timing diagram showing all the important signals and buses.

- (4) Stop the simulation, make the following changes, and run the simulator after each of them, watch their effects on different signals and record your notes:

- (A) What will happen if you change the instruction in line 1 to (MOV AX, 0FC00h), and try to fix any problem you will face.

- (B) Convert the program to move 16-bit in each cycle.

- (5) Draw the signal timing diagram for each case and state the affected signals?

## وصف مختبر تصميم منطق قابل للبرمجة

### 1. المعلومات العامة:

|                                |                                           |

|--------------------------------|-------------------------------------------|

| اسم المختبر و رقم المختبر:     | مختبر تصميم منطق قابل للبرمجة (مختبر 210) |

| اسم المقرر المرتبط:            | تصميم منطق قابل للبرمجة                   |

| القسم:                         | هندسة الحاسوب                             |

| عدد الساعات الأسبوعية للمختبر: | 3 ساعات                                   |

| عدد أسابيع الفصل الدراسي:      | 15 أسبوعاً                                |

| المستوى الدراسي:               | المستوى الثاني                            |

| المشرف على المختبر:            | أ.م.د. شوكت صباح خير الله                 |

### 2. وصف عام للمختبر:

تصميم وتحليل الدوائر الرقمية التتابعية (المترادفة) المعتمدة على الساعة، مثل المذبذبات وسجلات الإزاحة ، والعدادات ، وكاشفات الأنماط . كما يتناول المفاهيم المعمارية لأنواع مختلفة من أجهزة المنطق القابلة للبرمجة، والمخاطر في الدوائر المنطقية التوافقية وتقنيات التخلص منها. يشمل المقرر أيضاً تقنيات تصميم باستخدام مصفوفات البوابات المنطقية القابلة للبرمجة ميدانياً ( ) باستخدام لغة توصيف العتاد الإلكتروني عالية السرعة( ) ، ومقادمة في النمذجة والمحاكاة والتوليف ( باستخدام أدوات مثل Intel FPGAs أو Altera Xilinx أو). س يتم في هذا المقرر تقديم بنية اللغة، قواعد الكتابة، وأنواع البيانات المستخدمة في لغات توصيف العتاد ، واكتساب المهارة في كتابة أكواد HDL الأساسية.

### 3. أهداف المختبر:

الهدف الأساسي من هذا المقرر هو تعليم الطلاب المبادئ الأساسية للأنظمة الرقمية الحديثة، ولغة VHDL ، وتصميم المنطق القابل للبرمجة.

### 4. مخرجات التعلم:

بنهاية المختبر، يجب أن يكون الطالب قادرًا على:

- القدرة على تحديد وتحليل وحل المشكلات الهندسية المعقدة وفقاً لمبادئ الهندسة والعلوم والرياضيات.

- القدرة على اكتساب وتطبيق المعرفة الجديدة باستخدام استراتيجيات التعلم المناسبة.

- القدرة على المشاركة والعمل بشكل مهني وأخلاقي في مشاريع مختلفة ضمن فرق متعددة التخصصات.

- سيتمكن الطالب من تصميم وتحليل الدوائر الرقمية التتابعية المترادفة والتفاعلية مثل الفليب فلوب، سجلات الإزاحة، العداد، كاشفات الأنماط، وفهم تطبيقاتها.

- سيتعلم الطالب كيفية نمذجة الدوائر المنطقية التوافقية الأساسية مثل البوابات المنطقية، المبدلات، المفككـات، والدوائر التوافقية الأخرى باستخدام لغات توصيف العتاد (HDLs) مثل VHDL . كما سيكونون قادرين على

استخدام VHDL في ترميز الدوائر المنطقية التتابعية الأساسية، بما في ذلك الالاتشات، الفليب فلوب، آلات الحالة، السجلات، والعدادات.

- سيطّور الطلاب فهمًا متيناً للمفاهيم المعمارية والتقييات القابلة للبرمجة لأنواع مختلفة من أجهزة المنطق القابلة للبرمجة (PLDs) مثل الذاكرة القابلة للبرمجة ل القراءة فقط (PROM) ، منطق المصفوفة القابل للبرمجة (PAL) ، مصفوفة المنطق القابلة للبرمجة (GAL) ، تصميم المنطق القابل للبرمجة المعقد (CPLD) ، ومصفوفة البوابات القابلة للبرمجة ميدانياً (FPGA).

- سيفهم الطلاب المخاطر (Hazards) في الدوائر المنطقية التوافقية الناتجة عن نقص في النظام الرقمي أو تأثيرات خارجية. ويوجد نوعان رئيسيان من المخاطر: الساكنة والديناميكية، التي يمكن التخلص منها باستخدام طرق التخفيف المختلفة.

- سيكتسب الطلاب مهارات في محاكاة والتحقق من تصاميم لغات توصيف العتاد (HDL) سيتعلمون استخدام أدوات المحاكاة لاختبار وتصديق تصاميمهم قبل التنفيذ. كما سيكتسبون فهمًا لتقييات تجريد التصميم في HDL باستخدام النمذجة الهيكلية، وكيفية تقسيم التصميم المعقد إلى وحدات هرمية ووصف التوصيلات بينها.

- سيستكشف الطلاب عملية توليف العتاد (hardware synthesis) التي تحول وصفات HDL إلى تمثيلات على مستوى البوابات مناسبة للتنفيذ على أجهزة المنطق القابلة للبرمجة. سيتعلمون تقنيات التوليف واستراتيجيات التحسين لتحقيق الأداء المطلوب واستخدام الموارد بكفاءة

- سيتعلم الطلاب كيفية تحقيق الدوال المنطقية التوافقية وتنفيذ أنظمة المنطق التتابعية المتزامنة على أجهزة المنطق القابلة للبرمجة (PLD) التي تستخدم عادة مصفوفات منطقية كمنصة عتادية، مع إمكانيات تخزين منطقية ودخل/خرج قابل للبرمجة.

##### 5. الجدول الأسبوعي للتجارب:

| الأسبوع | عنوان التجربة                                                                                                                                                          | الأدوات / البرامج المستخدمة | الهدف الرئيسي                                                                                 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------|

| 1, 2    | التجربة 1 : (توليف وفهم عمل الالاتش، فليب- فلوب فلوب من نوع D، فليب-فلوب من نوع JK، فليب-فلوب من نوع T)                                                                | Proteus 8.13 software       | فهم المفاهيم الأساسية للفليب-فلوب باعتبارها وحدات أساسية أولية في الدوائر المنطقية التتابعية. |

| 3, 4    | التجربة 2 : (تصميم وفهم عمل سجلات الإزاحة ودوائر العد المتزامنة)                                                                                                       | Proteus 8.13 software       | فهم تصميم وعمل سجلات الإزاحة ودوائر العد المنطقية المتزامنة.                                  |

| 5, 6    | التجربة 3 : (استخدام محاكي Xilinx) أو (Altera أو Intel FPGAs) كأداة لتصميم النماذج، التوليف، والتحليل لنموذج المكونات التوافقية الأساسية: البوابات المنطقية، والمبدلات | Xilinx ISE 14.7 software    | تعريف الطلاب باستخدام محاكي VHDL مع لغة Xilinx ISE 14.7                                       |

|                                                                                                |                          |                                                                                                                 | VHDL باستخدام |

|------------------------------------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------|---------------|

| تنفيذ الوظائف المنطقية باستخدام دوائر المفکاك والمشفر باستخدام VHDL.                           | Xilinx ISE 14.7 software | التجربة 4 : (نمذجة المكونات التوافقية الأساسية: المفككات والمشفرات باستخدام VHDL)                               | 7, 8          |

| كتابة كود VHDL الهيكلي باستخدام المكونات (component).                                          | Xilinx ISE 14.7 software | التجربة 5 : (الهيكلية VHDL : Structural VHDL)                                                                   | 9, 10         |

| كتابة أوصاف كود VHDL التي تنفذ الالاتشات، الفليب-فلوب، سجلات الإزاحة، والعدادات باستخدام VHDL. | Xilinx ISE 14.7 software | التجربة 6 : (نمذجة المكونات التتابعية الأساسية: الالاتشات، الفليب-فلوب، سجلات الإزاحة، والعدادات باستخدام VHDL) | 11, 12        |

| كتابة أوصاف كود VHDL التي تنفذ آلات الحالة (State Machines).                                   | Xilinx ISE 14.7 software | التجربة 7 : (آلة الحالة باستخدام VHDL)                                                                          | 13, 14        |

|                                                                                                |                          | الامتحان النهائي                                                                                                | 15            |

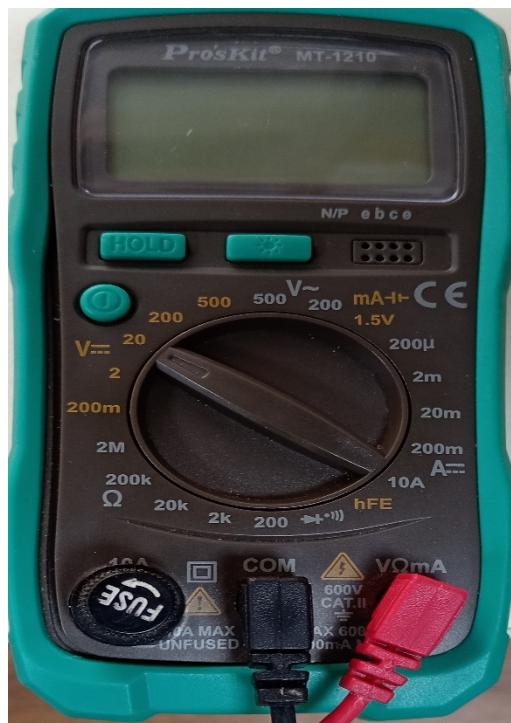

#### 6. الأدوات والمعدات المستخدمة:

- برنامج Xilinx ISE 14.7

- برنامج Proteus 8.13

- جهاز Spartan-3 FPGA

- جهاز FPGA Spartan-3E

- أسلاك

- فولتميتر

#### 7. دليل السلامة:

- التأكد من فصل التيار الكهربائي عند توصيل الأجهزة.

- عدم لمس المنافذ الكهربائية أو مكونات الجهاز دون إذن المشرف.

- الالتزام بالهدوء وتنظيم الكابلات لتجنب الحوادث.

#### 8. آلية التقييم:

| عنصر التقييم             | النسبة |

|--------------------------|--------|

| تقارير التجارب الأسبوعية | % 10   |

| المشروع العملي/المختبر   | % 6    |

| الامتحان العملي النهائي  | % 10   |

#### 9. المراجع والمصادر:

- Mod Modern digital design by Richard S. Sandige (McGraw-Hill)

- Voinci A. pedroni, "Circuit design with VHDL", MIT press, Cambridge, London 2004.

- Thom A.S. "digital with CPLA application and VHDL.

- Introduction to Logic Design, 3rd edition, Alan Marcovitz, McGraw-Hill, 2010.

#### 10. المرفقات:

نموذج تقرير التجربة

مهمة/واجب التجربة

## وصف مختبر الإلكترونيك التناهري

### 1. المعلومات العامة:

|                                |                                        |

|--------------------------------|----------------------------------------|

| اسم المختبر و رقم المختبر:     | مختبر الإلكترونيك التناهري (مختبر 108) |

| اسم المقرر المرتبط:            | Analog Electronics                     |

| القسم:                         | هندسة الحاسوب                          |

| عدد الساعات الأسبوعية للمختبر: | 6 ساعات                                |

| عدد أسابيع الفصل الدراسي:      | 15 أسبوعاً                             |

| المستوى الدراسي:               | المستوى الثاني                         |

| المشرف على المختبر:            | أ. م.د. ربيع موفق حاجم                 |

### 2. وصف عام للمختبر:

مختبر الإلكترونيات التناهيرية هو بيئة تعليمية وتجريبية تستخدم لتدريس وتطبيق مبادئ الإلكترونيات التناهيرية، التي تتعامل مع الإشارات التي تأخذ قيماً مستمرة مثل التيار أو الجهد الكهربائي. يهدف المختبر إلى تعليم الطلاب كيفية تصميم وتحليل الدوائر الإلكترونية الأساسية التي تستخدم المكونات التناهيرية مثل المقاومات، والمكثفات، والترانزستورات، والموحدات (الثنائيات)، ومضخمات العمليات.

### 3. أهداف المختبر:

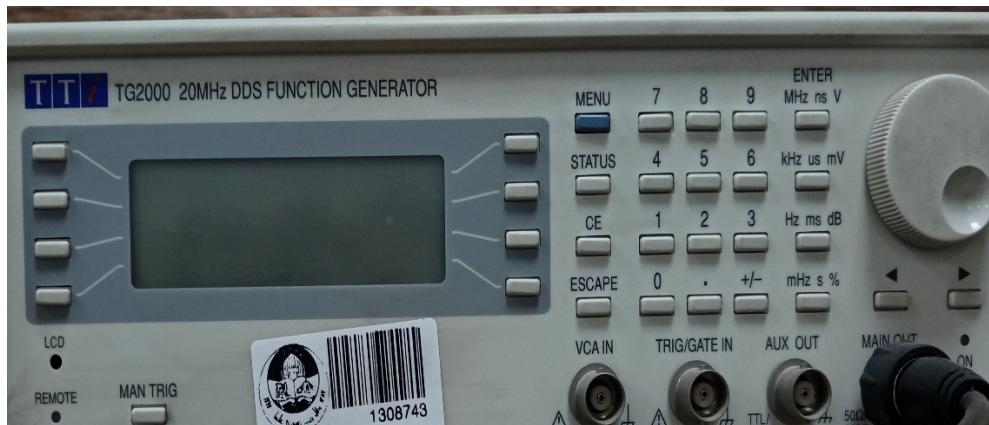

- في مختبر الإلكترونيات التناهيرية، يتم تنفيذ العديد من التجارب العملية التي تساعد الطلاب على فهم كيفية عمل الدوائر، وكيفية استجابة المكونات التناهيرية للإشارات المختلفة. يمكن للطلاب قياس التيارات والجهود وتحليل خصائص الموجات المتولدة باستخدام أجهزة مثل الملتمتر، والأوسيلوسكوب، ومولادات الإشارة، وأجهزة قياس التردد.

### 4. مخرجات التعلم:

- بنهاية المختبر، يجب أن يكون الطالب قادرًا على تطبيق الدوائر التالية:

- دوائر قص الثنائيات، تثبيت الثنائيات، دوائر التقويم.

- دوائر تضخيم الترانزستور (CC, CB, CE).

- دوائر OP AMP.

- دوائر التضخيم الأساسي لمضخم التشغيل OP AMP (متتابع الجهد، والجمع، والطرح الدائرة التفاضلية، ودائرة التكامل).

5. الجدول الأسبوعي للتجارب:

| الأسبوع | عنوان التجربة                      | الأدوات / البرامج المستخدمة                                                                                                   | الهدف الرئيسي                                                                                                            |

|---------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

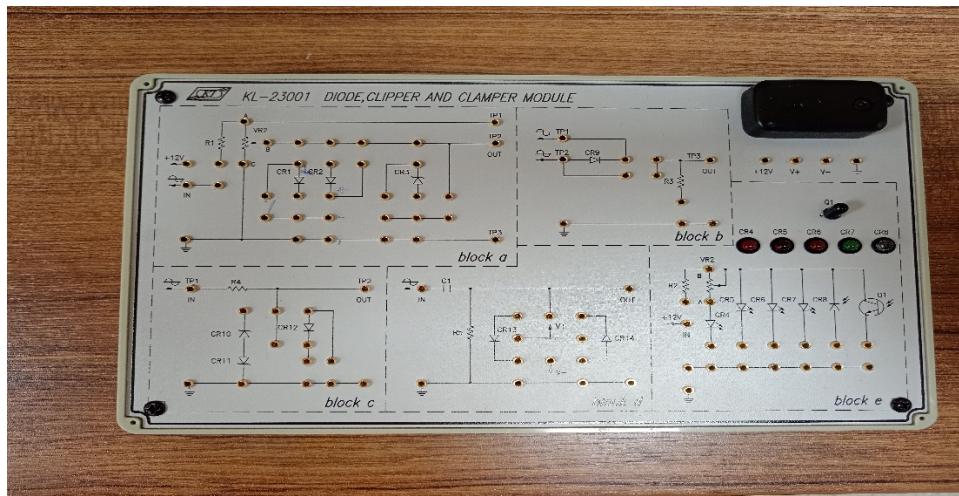

| 1       | مقدمة في خصائص الثنائيات وصلة.(PN) | مخبر الدوائر الخطية-KI-200<br>وحدة التجارب: طقم-KI-23001<br>مقياس متعدد رقمي، راسم ذبذبات، ومولد إشارة، وأدوات يدوية أساسية.  | فهم خصائص كل نوع من أجهزة الثنائيات.<br>التعرف على مواصفات كل نوع من أجهزة الثنائيات.<br>تعلم كيفية اختبار خصائص كل نوع. |

| 2       | دائرة قص الثنائيات.                | مخبر الدوائر الخطية-KI-200<br>وحدة التجارب: طقم-KI-23001<br>مقياس متعدد رقمي، راسم ذذبذبات، ومولد إشارة، وأدوات يدوية أساسية. | فهم مبدأ تشغيل دائرة قص الصمام الثنائي                                                                                   |

| 3       | دائرة تثبيت الثنائيات.             | مخبر الدوائر الخطية-KI-200<br>وحدة التجارب: طقم-KI-23001<br>مقياس متعدد رقمي، راسم ذذبذبات، ومولد إشارة، وأدوات يدوية أساسية. | فهم مبدأ تشغيل دائرة تثبيت الصمام الثنائي                                                                                |

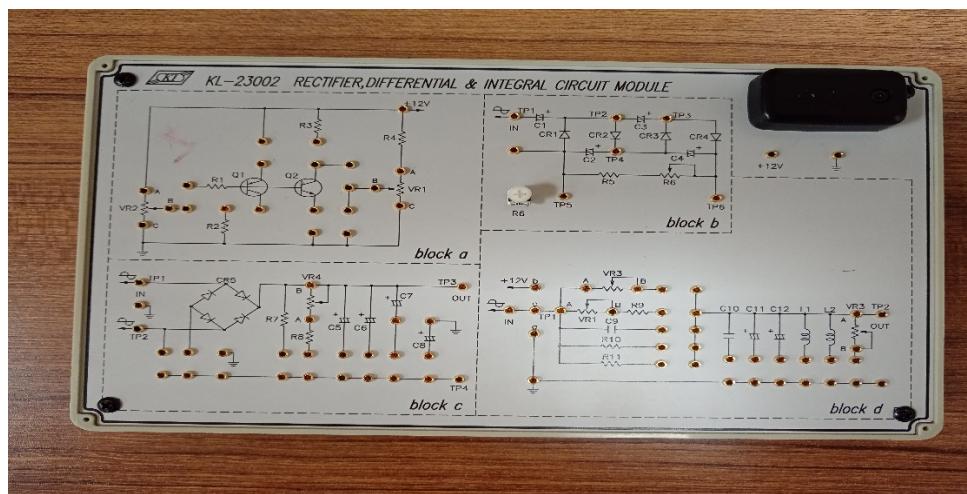

| 4       | دائرة التقويم.                     | مخبر الدوائر الخطية-KI-200<br>وحدة التجارب: طقم-KI-23001<br>مقياس متعدد رقمي، راسم                                            | فهم مبادئ وخصائص مقوم الموجة النصفية والموجة الكاملة والجسر.                                                             |

|   |                                                                                                                                                                                                                                                 |                                                                        |  |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--|

|   | ذذبات، ومولد إشارة، وأدوات يدوية أساسية.                                                                                                                                                                                                        |                                                                        |  |

| 5 | مخبر الدوائر الخطيـة-KI-200<br>وحدة التجارب: طقم-KI-23021<br>مقياس متعدد رقمي، راسم<br>ذذبات، ومولد إشارة،<br>وأدوات يدوية أساسية.<br>فهم بنية ورموز الترانزستورات<br>وخصائص الترانزستورات                                                      | خاصـص الترانـزـتـور.                                                   |  |

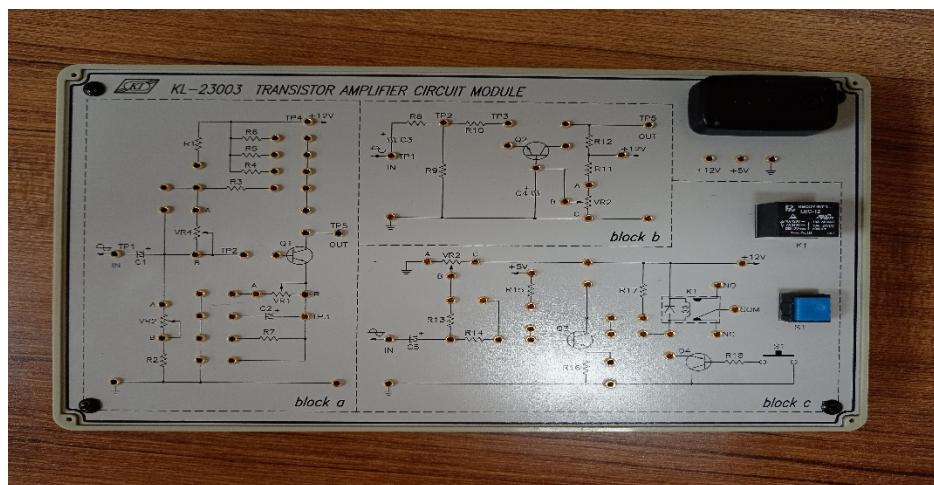

| 6 | مخبر الدوائر الخطيـة-KI-200<br>وحدة التجارب: طقم-KI-23002<br>مقياس متعدد رقمي، راسم<br>ذذبات، ومولد إشارات،<br>وأدوات يدوية أساسية.<br>فهم الخصائص الأساسية لكل دائرة<br>تضخيم ومعنى أوضاع التشغيل<br>الثلاثة للترانزستور (تضخيم CE،<br>CB)، CC | دائـرة تضـخـيم التـرانـزـتـور.                                         |  |

| 7 | مخبر الدوائر الخطيـة-KI-200<br>وحدة التجارب: طقم-KI-23003<br>مقياس متعدد رقمي، راسم<br>ذذبات، ومولد إشارات،<br>وأدوات يدوية أساسية.<br>فهم خصائص دائرة الترانزستور<br>لمضمـخـ الـبـاعـثـ المـشـترـكـ (CE).                                      | دائـرة تضـخـيم التـرانـزـتـور:<br>مضـخـ الـبـاعـثـ المـشـترـكـ<br>(CE) |  |

| 8 | مخبر الدوائر الخطيـة-KI-200<br>وحدة التجارب: طقم-KI-23003<br>انـحـيـازـ الـبـاعـثـ الذـاتـيـ.                                                                                                                                                   | انـحـيـازـ الـبـاعـثـ الذـاتـيـ.                                       |  |

|                                                                                             |                                                                                                                                             |                                                            |    |

|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----|

|                                                                                             | مقياس متعدد رقمي، راسم<br>ذبذبات، ومولد إشارات،<br>وأدوات يدوية أساسية.                                                                     |                                                            |    |

| فهم خصائص مكبر القاعدة<br>المشتركة (CB)                                                     | مختبر الدوائر الخطية-K1<br>200<br>وحدة التجارب: طقم-kl-<br>23003<br>مقياس متعدد رقمي، راسم<br>ذبذبات، ومولد إشارات،<br>وأدوات يدوية أساسية. | دائرة تضخيم الترانزستور:<br>مضخم القاعدة المشتركة<br>(CB). | 9  |

| فهم خصائص مكبر المجمع<br>المشترك .(C)                                                       | مختبر الدوائر الخطية-K1<br>200<br>وحدة التجارب: طقم-kl-<br>23003<br>مقياس متعدد رقمي، راسم<br>ذبذبات، ومولد إشارات،<br>وأدوات يدوية أساسية. | دائرة تضخيم الترانزستور:<br>مضخم المجمع المشترك<br>(CC).   | 10 |

| فهم مبدأ عمل مكبرات الصوت مع<br>أنواع مختلفة من الاقتران، دوائر<br>مكبر الصوت OTL و OCL.    | مختبر الدوائر الخطية-K1<br>200<br>وحدة التجارب: طقم-kl-<br>23005<br>مقياس متعدد رقمي، راسم<br>ذبذبات، ومولد إشارات،<br>وأدوات يدوية أساسية  | دائرة تضخيم متعدد المراحل.                                 | 11 |

| فهم الخصائص الأساسية لمكبر<br>التشغيل ZO و ZI و BW و طريقة<br>ضبط جهد الإزاحة لمكبر التشغيل | مختبر الدوائر الخطية-K1<br>200<br>وحدة التجارب: طقم-kl-<br>23012                                                                            | الخصائص الأساسية لمضخم<br>التشغيل.(OPA AMP).               | 12 |

|                                                                        |                                                                                                                                     |                                                                           |    |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----|

|                                                                        | مقاييس متعدد رقمي، راسم<br>ذبذبات، ومولد إشارة،<br>وأدوات يدوية أساسية                                                              |                                                                           |    |

| فهم الخصائص الأساسية لمضخم التشغيل (متتابع الجهد، والجمع، والطرح).     | مختبر الدوائر الخطية-KI-200<br>وحدة التجارب: طقم-kl-23013<br>مقاييس متعدد رقمي، راسم<br>ذبذبات، ومولد إشارة،<br>وأدوات يدوية أساسية | التضخيم الأساسي لمضخم التشغيل OP AMP (متتابع الجهد، والجمع، والطرح).      | 13 |

| فهم الخصائص الأساسية لمضخم التشغيل (الدائرة التقاضلية ودائرة التكامل). | مختبر الدوائر الخطية-KI-200<br>وحدة التجارب: طقم-kl-23013<br>مقاييس متعدد رقمي، راسم<br>ذبذبات، ومولد إشارة،<br>وأدوات يدوية أساسية | التضخيم الأساسي لمضخم التشغيل OP AMP (الدائرة التقاضلية، ودائرة التكامل). | 14 |

| مراجعة شاملة لجميع مواضيع المختبر                                      | جميع المعدات                                                                                                                        | الأسبوع التحضيري قبل الامتحان النهائي.                                    | 15 |

#### 6. الأدوات والمعدات المستخدمة:

- مختبر الدوائر الخطية KI-200

- وحدة التجارب: طقم kl-23013

- وحدة التجارب: طقم kl-23012

- وحدة التجارب: طقم kl-23005

- وحدة التجارب: طقم kl-23003

- وحدة التجارب: طقم kl-23002

- وحدة التجارب: طقم KI-23001

- مقاييس متعدد رقمي، راسم موجات، ومولد إشارة، و أدوات يدوية أساسية

## 7. دليل السلامة:

- التأكد من فصل التيار الكهربائي عند توصيل الأجهزة.

- عدم لمس المنافذ الكهربائية أو مكونات الشبكة دون إذن المشرف.

- الالتزام بالهدوء وتنظيم الكابلات لتجنب الحوادث.

- استخدام البرنامج المحاكي لتجارب التوجيه قبل التجريب على الأجهزة الحقيقية.

## 8. آلية التقييم:

| عنصر التقييم             | النسبة |

|--------------------------|--------|

| الحضور والمشاركة         | 10%    |

| تقارير التجارب الأسبوعية | 30%    |

| الاختبارات القصيرة       | 20%    |

| الامتحان العملي النهائي  | 30%    |

| المشروع العملي           | 10%    |

## 9. المراجع والمصادر:

Electronic Devices, Thomas L. Floyd, 7th edition, 2017 •

## 10. المرفقات:

## مختبر الإلكتروني التمازجي

**: (Linear Circuit Lab.)**

**مولد إشارة:**

مقیاس متعدد رقمهی:

راسم موچات:

• وحدة التجارب: طقم 1 KL-23001

• وحدة التجارب: طقم 2 KL-23002

• وحدة التجارب: طقم 3 KL-23003

## وصف مختبر الكترونيات رقمية

### 1. المعلومات العامة:

|                                |                              |

|--------------------------------|------------------------------|

| اسم المختبر و رقم المختبر:     | الكترونيات رقمية (مختبر 111) |

| اسم المقرر المرتبط:            | الكترونيات رقمية             |

| القسم:                         | هندسة الحاسوب                |

| عدد الساعات الأسبوعية للمختبر: | 3 ساعات                      |

| عدد أسابيع الفصل الدراسي:      | 15 أسبوعاً                   |

| المستوى الدراسي:               | المستوى الثاني               |

| المشرف على المختبر:            | م. مصر احمد حمودي حسين       |

### 2. وصف عام للمختبر:

يهدف مختبر إلكترونيك الرقمي إلى تعزيز المفاهيم النظرية التي تم تناولها في محاضرات مقرر الإلكترونيات الرقمية، من خلال تطبيقات عملية باستخدام الأدوات اللازمة لتحليل وتصميم الدوائر والأنظمة الرقمية. يوفر المختبر بيئة تفاعلية تُمكّن الطلاب من اكتساب أساس متين في كل من المجالين الرقمي والإلكتروني.

### 3. أهداف المختبر:

- تدريب الطلاب على تصميم وإعداد الدوائر والأنظمة الرقمية.

- التعرف على جميع أنواع الدوائر الإلكترونية الرقمية والاختلاف بينها

- استخدام المفاهيم الأساسية للتحليل الكهربائي والإلكتروني لتحديد استهلاك الطاقة وعدد دوائر الأحمال ومستويات الجهد المنطيقي للبوابة المنطقية.

- اختيار التصميم المنطقي المناسب من الأنواع المختلفة لعائلات البوابات المنطقية

- القدرة على تقييم المقاييس الكهربائية والمنطقية لأي دائرة منطقية رقمية

### 4. مخرجات التعلم:

بنهاية المختبر، يجب أن يكون الطالب قادرًا على:

- تسمية جميع أنواع الدوائر الإلكترونية الرقمية والاختلاف بينها.

- اختيار التصميم المنطقي المناسب من الأنواع المختلفة لعائلات البوابات المنطقية.

- تصميم دائرة منطقية رقمية جديدة لأداء مهمة معينة

- توثيق التجارب وإعداد تقارير احترافية.

- العمل ضمن فريق لحل مشاكل الأنظمة الرقمية.

5. الجدول الأسبوعي للتجارب:

| الأسبوع | عنوان التجربة                                                                  | الأدوات / البرامج المستخدمة | الهدف الرئيسي                                                                                        |

|---------|--------------------------------------------------------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------|

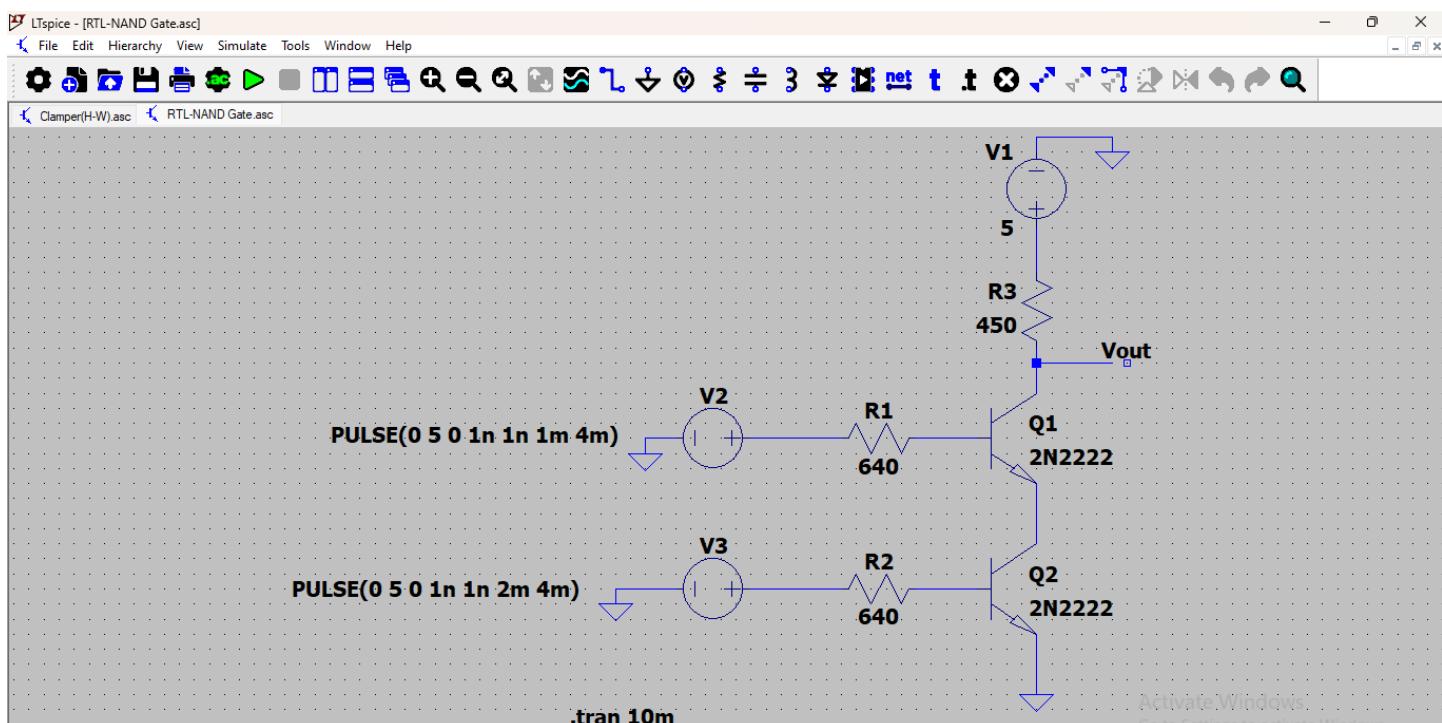

| 1       | مقدمة إلى LTSpice                                                              | LTSpice                     | التعرف على بيئة محاكاة LTSpice واستخدامها في تحليل وتصميم الدوائر الإلكترونية الرقمية.               |

| 2       | تصميم البوابات منطقية باستخدام (Resistor diode logic RDL)                      | LTSpice                     | بناء ومحاكاة دوائر منطقية بسيطة تعتمد على المقاومات والدايوودات لتنفيذ الوظائف المنطقية.             |

| 3       | تصميم البوابات منطقية باستخدام (Resistor transistor logic RTL)                 | LTSpice                     | تصميم دوائر منطقية تعتمد على المقاومات والترانزستورات لإنتاج البوابات الأساسية مثل AND و OR و NOT.   |

| 4       | تصميم البوابات منطقية باستخدام (Diode transistor logic DTL)                    | LTSpice                     | محاكاة دوائر منطقية تستخدم الدايوودات للربط والترانزستورات للتكيير من أجل تنفيذ الوظائف المنطقية.    |

| 5       | تصميم البوابات منطقية باستخدام (Transistor transistor logic TTL)               | LTSpice                     | بناء دوائر منطقية تعتمد فقط على الترانزستورات لتنفيذ عمليات منطقية سريعة وفعالة.                     |

| 6       | تصميم البوابات منطقية باستخدام (Emitter coupled logic ECL, I2L)                | LTSpice                     | استكشاف تصميم بوابات منطقية عالية السرعة باستخدام تقنيات ECL و I2L.                                  |

| 7       | تصميم البوابات منطقية باستخدام (NMOS and PMOS logic circuits)                  | LTSpice                     | تنفيذ ومحاكاة بوابات منطقية باستخدام الترانزستورات من نوع NMOS و PMOS.                               |

| 8       | تصميم البوابات منطقية باستخدام (Complementary Metal Oxide CMOS logic circuits) | LTSpice                     | تصميم بوابات منطقية فعالة في استهلاك الطاقة باستخدام تقنية CMOS التي تجمع بين NMOS و PMOS.           |

| 9       | Term exam                                                                      |                             | تقييم شامل لمهارات الطالب في تصميم وتحليل دوائر منطقية باستخدام التقنيات التي تم تغطيتها في المختبر. |

|                                                                                                      |              |                                                                 |    |

|------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------------|----|

| بناء ومحاكاة دوائر منطقية تسلسلية باستخدام ترانزستورات MOS لتنفيذ وظائف الذاكرة.                     | LTS defense  | تصميم الدوائر المنطقية باستخدام (Sequential MOS logic circuits) | 10 |

| تحليل وتصميم دوائر منطقية تعتمد على التغذية الراجعة لتحقيق الثبات والمنطق الثنائي.                   | LTS defense  | تصميم الدوائر المنطقية باستخدام (Regenerative logic circuits)   | 11 |

| التعرف على بنية وعمل دوائر الذاكرة النصف ناقلة مثل RAM و ROM وتصميمها باستخدام أدوات المحاكاة.       | LTS defense  | تصميم الدوائر المنطقية باستخدام (Semiconductor memories)        | 12 |

| دمج المهارات المكتسبة في مشروع نهائي                                                                 | جميع الأدوات | مراجعة شاملة ومناقشة المشروع العملي                             | 13 |

| تقييم شامل لمهارات الطالب في تصميم وتحليل دوائر منطقية باستخدام التقنيات التي تم تغطيتها في المختبر. |              | Final exam                                                      | 14 |

#### 6. الأدوات والمعدات المستخدمة:

- حواسيب مختبرية

- برنامج LTS defense

#### 7. دليل السلامة:

##### • استخدام جهاز الحاسوب بطريقة آمنة وصحيحة:

اجلس في وضعية مريحة، وتجنب إجهاد العينين باستخدام إضاءة مناسبة وأخذ فترات راحة قصيرة أثناء العمل الطويل على البرنامج.

##### • الالتزام بتعليمات المشرف أو المدرس بدقة:

اتبع الخطوات التعليمية بدقة أثناء تصميم الدوائر وتجنب تنفيذ محاكاة بدون مراجعة التوصيات والمعلمات، لتفادي حدوث نتائج خاطئة أو ارتباك أثناء التجربة.

##### • الحفاظ على ملفات العمل وتنظيمها:

احرص على حفظ ملفات التجارب باسم مناسب وفي مكان منظم على جهازك لتسهيل مراجعتها لاحقاً، وتجنب حذف أو تعديل ملفات زملائك دون إذن.

## 8. آلية التقييم:

| عنصر التقييم            | النسبة |

|-------------------------|--------|

| الحضور والمشاركة        | 10%    |

| الامتحان النصف النهائي  | 30%    |

| الاختبارات القصيرة      | 20%    |

| الامتحان العملي النهائي | 30%    |

| المشروع العملي          | 10%    |

## 9. المراجع والمصادر:

- “Digital Integrated Circuits Analysis and Design” by: John E. Ayers.2004

- 1“ .Analysis and Design of Digital Integrated Circuits” by: David A. Hodges. 1988

- 2.Lab Manual , LTSPICE Design Tool.

## 10. المرفقات:

- خطة العمل الأسبوعية

- تعليمات استخدام LTSpice

## وصف مختبر برمجة الكائنات الموجهة

### 1. المعلومات العامة:

|                                |                                                                 |

|--------------------------------|-----------------------------------------------------------------|

| اسم المختبر و رقم المختبر:     | مختبر برمجة الكائنات الموجهة (مختبر 312)                        |

| اسم المقرر المرتبط:            | برمجة الكائنات الموجهة                                          |

| القسم:                         | هندسة الحاسوب                                                   |

| عدد الساعات الأسبوعية للمختبر: | 3 ساعات                                                         |

| عدد أسابيع الفصل الدراسي:      | 15 أسبوعاً                                                      |

| المستوى الدراسي:               | المستوى الثاني                                                  |

| المشرف على المختبر:            | أ.م. د. توركان احمد خليل & سحر خالد احمد + م.م. هبة ضياء النعمة |

### 2. وصف عام للمختبر:

يهدف مختبر البرمجة بالكائنات الموجهة (OOP) إلى تزويد الطلبة بالخبرة العملية في تصميم وتنفيذ البرمجيات باستخدام مبادئ البرمجة بالكائنات باستخدام لغة C++. يدعم المختبر الجانب النظري للمقرر ويركز على التصميم المعياري، إعادة استخدام الشيفرة، وقابلية التوسيع. سيقوم الطلبة بتنفيذ مهام عملية تتضمن التغليف، الوراثة، تعدد الأشكال، والتجريد لحل المشكلات البرمجية بكفاءة.

### 3. أهداف المختبر:

- تعزيز فهم مفاهيم البرمجة بالكائنات الموجهة من خلال التطبيق العملي.

- تمكين الطلبة من تنفيذ برامج C++ باستخدام مبادئ OOP مثل: الصنوف، الكائنات، التغليف، الوراثة، وتعدد الأشكال.

- تطوير قدرة الطلبة على تصميم برمجيات قابلة للصيانة والتوسيع.

- تدريب الطلبة على استخدام الصنوف المجردة والواجهات في سيناريوهات واقعية.

- تمكين الطلاب من تحليل و اختيار الهياكل المناسبة للمشكلات

- مساعدة الطلاب على تحديد الهيكل الأنسب للمشكلة البرمجية من حيث الكفاءة والمرنة.

- تشجيع التفكير التحليلي وتجزئة المشكلات المعقدة إلى وحدات صغيرة قابلة للحل باستخدام هيكل بيانات مناسبة.

- تمكين الطالب من دمج أكثر من هيكل بيانات في برنامج عملی متکامل كمقدمة لمشاريع التخرج أو التطبيقات الواقعية.

#### 4. مخرجات التعلم:

بنهاية المختبر، يجب أن يكون الطالب قادرًا على:

- تحليل وحل المشكلات البرمجية باستخدام OOP في C++.

- تصميم وتنفيذ برامج كائنية التوجّه مع التركيز على القابلية لإعادة الاستخدام والصيانة.

- تطبيق التغليف، الوراثة، وتعدد الأشكال ضمن تسلسل هرمي للصفوف.

- تنفيذ الصنف المجردة وتحميل الدوال (Overloading).

- التعامل مع الاستثناءات وتصحيح الشيفرة البرمجية.

- التعاون بفعالية في مشاريع برمجية تعتمد على العمل الجماعي.

#### 5. الجدول الأسبوعي للتجارب:

| الأسبوع | عنوان التجربة           | الأدوات / البرامج المستخدمة | الهدف الرئيسي                     |

|---------|-------------------------|-----------------------------|-----------------------------------|

| 1       | المقدمة ومراجعة البرمجة | C++ / Code::Blocks          | إعداد البيئة ومراجعة الأساسيات    |

| 2       | الكائنات والصفوف        | C++ / Code::Blocks          | فهم هيكل الكائنات                 |

| 3       | التجريد البياني         | C++ / Code::Blocks          | فصل الواجهة عن التنفيذ            |

| 4       | التغليف والإخفاء        | C++ / Code::Blocks          | حماية بيانات الصنف                |

| 5       | المنشئون والمدمرون      | C++ / Code::Blocks          | إدارة دورة حياة الكائن            |

| 6       | دوال الصنف              | C++ / Code::Blocks          | تعريف واستدعاء الدوال             |

| 7       | التحميل الزائد للدوال   | C++ / Code::Blocks          | إنشاء نسخ متعددة من الدوال        |

| 8       | الوراثة                 | C++ / Code::Blocks          | إنشاء تسلسلات هرمية للصفوف        |

| 9       | تعدد الأشكال            | C++ / Code::Blocks          | إتاحة السلوك المرن والдинاميكي    |

| 10      | الصنف المجردة           | —                           | تعريف قوالب عامة للصفوف الفرعية   |

| 11      | الدوال المجردة          | C++ / Code::Blocks          | فرض تنفيذ الصنف الفرعي            |

| 12      | التعامل مع الاستثناءات  | C++ / Code::Blocks          | معالجة الأخطاء وقت التنفيذ        |

| 13      | عرض المشروع/الدعم       | C++ / Code::Blocks          | تقييم الطلبة وتقديم المساعدة      |

| 14      | مراجعة واستعداد نهائي   | —                           | مراجعة ومساعدة في المشروع النهائي |

#### 6. الأدوات والمعدات المستخدمة:

- حواسيب مختبرية

- C++ / Code::Blocks

## 7. دليل السلامة:

- التأكد من فصل التيار الكهربائي عند توصيل الأجهزة.

- عدم لمس المنافذ الكهربائية أو مكونات الشبكة دون إذن المشرف.

- الالتزام بالهدوء وتنظيم الكابلات لتجنب الحوادث.

## 8. آلية التقييم:

| عنصر التقييم             | النسبة |

|--------------------------|--------|

| تقارير التجارب الأسبوعية | %5     |

| الاختبارات القصيرة       | %5     |

| الامتحان العملي النهائي  | %10    |

| المشروع العملي           | %10    |

## 9. المراجع والمصادر:

Object-Oriented Programming in C++, Fourth Edition, by , Robert Lafore , Waite Group,Sams Publishing,2002.

C++ programming an object oriented approach,

by Admin , 2022 .

## 10. المرفقات:

صور المختبر

## وصف مختبر هياكل البيانات

### 1. المعلومات العامة:

|                                |                                                 |

|--------------------------------|-------------------------------------------------|

| اسم المختبر و رقم المختبر:     | مختبر هياكل البيانات (مختبر 312)                |

| اسم المقرر المرتبط:            | هياكل البيانات                                  |

| القسم:                         | هندسة الحاسوب                                   |

| عدد الساعات الأسبوعية للمختبر: | 3 ساعات                                         |

| عدد أسابيع الفصل الدراسي:      | 15 أسبوعاً                                      |

| المستوى الدراسي:               | المستوى الثاني                                  |

| المشرف على المختبر:            | أ.م. د. توركان احمد خليل + م.م. هبة ضياء النعمة |

### 2. وصف عام للمختبر:

يهدف مختبر شبكات الحاسوب إلى تعزيز المفاهيم النظرية التي تم تناولها في محاضرات مقرر شبكات الحاسوب، من خلال تطبيقات عملية ومحاكاة باستخدام أدوات وبرمجيات مخصصة لتصميم وتحليل الشبكات. يوفر المختبر بيئة تفاعلية تمكن الطلاب من اكتساب مهارات تركيب وإعداد الشبكات السلكية واللاسلكية، بالإضافة إلى إعداد بروتوكولات التوجيه وتأمين الشبكات.

### 3. أهداف المختبر:

- تعزيز فهم المفاهيم النظرية من خلال التطبيق العملي

- تمكين الطلاب من ربط المفاهيم النظرية لهياكل البيانات بالتطبيقات العملية باستخدام لغة C++.

- تطوير مهارات البرمجة باستخدام هياكل البيانات المختلفة

- تدريب الطلاب على كتابة برامج تعتمد على المصفوفات، القوائم المرتبطة، المكدسات، الطوابير، الأشجار، الرسوم البيانية، وتجزئة.

- تمكين الطلاب من تحليل و اختيار الهياكل المناسبة للمشكلات

- مساعدة الطلاب على تحديد الهيكل الأنسب للمشكلة البرمجية من حيث الكفاءة والمونة.

- تشجيع التفكير التحليلي وتجزئة المشكلات المعقدة إلى وحدات صغيرة قابلة للحل باستخدام هياكل بيانات مناسبة.

- تمكين الطالب من دمج أكثر من هيكل بيانات في برنامج عملي متكملاً كمقدمة لمشاريع التخرج أو التطبيقات الواقعية.

### 4. مخرجات التعلم:

بنهاية المختبر، يجب أن يكون الطالب قادرًا على:

- فهم المفاهيم الأساسية لهيكل البيانات

- تعريف وتطبيق الهيكل الخطية وغير الخطية (مثل المصفوفات، المكدسات، الطوابير، القوائم المرتبطة، الأشجار، الرسوم البيانية).

- القدرة على كتابة برامج باستخدام C++ لتنفيذ هيكل البيانات

- تطوير وتنفيذ برامج هيكل بيانات واقعية باستخدام لغة C++

- تصميم وتنفيذ هيكل بيانات مناسبة لحل مشكلات برمجية محددة

- اختيار الهيكل الأنسب (Stack, Queue, Tree, Graph) تبعًا لنوع المشكلة.

- تطبيق مبادئ البرمجة الكائنية (OOP)

- استخدام الفئات (Classes) والكائنات لتنظيم الكود وتغليف البيانات.

- استخدام العودية (Recursion) في حل المشكلات الكلاسيكية

- تنفيذ خوارزميات بحث وفرز فعالة

- تنفيذ وتحليل خوارزميات مثل: Selection Sort، Bubble Sort، Binary Search وغيرها.

- تحليل الأداء والكافأة الزمنية لهيكل البيانات والخوارزميات

- تمثيل العلاقات المعقدة باستخدام الأشجار والرسوم البيانية

- بناء شجرة ثنائية والقيام بعمليات الإدراج، الحذف، والاجتياز (Traversal).

- تمثيل الرسوم البيانية باستخدام مصفوفات وقوائم المجاورة.

- فهم واستخدام تقنيات التجزئة (Hashing)

## 5. الجدول الأسبوعي للتجارب:

| الأسبوع | عنوان التجربة                                                            | الأدوات / البرامج المستخدمة | الهدف الرئيسي                                    |

|---------|--------------------------------------------------------------------------|-----------------------------|--------------------------------------------------|

| 1       | تنفيذ برامج: المصفوفات، الدوال، التراكيب، الكائنات(Classes)              | C++ / Code::Blocks          | مراجعة المفاهيم الأساسية في البرمجة باستخدام C++ |

| 2       | العودية في البرمجة وحل المشكلات: دوال مثل Factorial والمشكلات الكلاسيكية | C++ / Code::Blocks          | فهم العودية وتطبيقاتها في الحلول البرمجية        |

| 3       | المكدسات: (Stacks) تعريف وتنفيذها باستخدام ADT المصفوفات والتراكيب       | C++ / Code::Blocks          | إنشاء Stack باستخدام مصفوفة وتنفيذ push/pop      |

| 4       | المكدسات: (Stacks) تنفيذ باستخدام القوائم المرتبطة                       | C++ / Code::Blocks          | تصميم Stack ديناميكي باستخدام Linked List        |

| 5       | الطوابير: (Queues) تعريف                                                 | C++ / Code::Blocks          | تنفيذ Queue باستخدام Array وتحليل                |

|                                                          |                    |                                                                        |    |

|----------------------------------------------------------|--------------------|------------------------------------------------------------------------|----|

| عملياته                                                  |                    | وتنفيذ باستخدام المصفوفات<br>والتراكيب ADT                             |    |

| تصميم Queue ديناميكي باستخدام<br>Linked List             | C++ / Code::Blocks | الطاوبير (Queues): تنفيذ<br>باستخدام القوائم المرتبطة                  | 6  |

| تنفيذ Circular Queue وحل مشكلة<br>الامتداء الزائف        | C++ / Code::Blocks | الطاوبير الدائري: تنفيذ باستخدام<br>المصفوفات والتراكيب                | 7  |

| تصميم Circular Queue باستخدام<br>Linked List             | C++ / Code::Blocks | الطاوبير الدائري: تنفيذ باستخدام<br>القوائم المرتبطة                   | 8  |

| : Inorder, Preorder, Postorder<br>تنفيذ خوارزميات اجتياز | C++ / Code::Blocks | اجتياز الأشجار (Trees)<br>تطبيقات على Traversals):<br>الأشجار الثنائية | 9  |

| تقييم عملي لمهارات الطالب في النصف<br>الأول              | —                  | امتحان منتصف الفصل-Mid-<br>term Exam)                                  | 10 |

| تمثيل الرسوم البيانية وتطبيقات على<br>BFS / DFS          | C++ / Code::Blocks | نظرية الرسوم البيانية (Graph<br>Theory)                                | 11 |

| تنفيذ جدول تجزئة بسيط وفهم<br>(Collision)اصطدام          | C++ / Code::Blocks | تقنيات التجزئة (Hashing<br>Techniques)                                 | 12 |

| تطبيق خوارزميات مثل, Selection, Binary Search            | C++ / Code::Blocks | تقنيات الترتيب والبحث<br>& Searching)                                  | 13 |

| تقييم شامل لمهارات الطالب العملية في<br>المقرر           | —                  | الامتحان النهائي(Final Exam)                                           | 14 |

## 6. الأدوات والمعدات المستخدمة:

- حواسيب مختبرية

- برنامج C++ / Code::Blocks

## 7. دليل السلامة:

- التأكد من فصل التيار الكهربائي عند توصيل الأجهزة.

- عدم لمس المنافذ الكهربائية أو مكونات الشبكة دون إذن المشرف.

- الالتزام بالهدوء وتنظيم الكابلات لتجنب الحوادث.

- استخدام البرنامج المحاكي لتجارب التوجيه قبل التجريب على الأجهزة الحقيقية.

#### 8. آلية التقييم:

| عنصر التقييم             | النسبة |

|--------------------------|--------|

| تقارير التجارب الأسبوعية | % 5    |

| الاختبارات القصيرة       | % 5    |

| الامتحان العملي النهائي  | % 10   |

| المشروع العملي           | % 10   |

#### 9. المراجع والمصادر:

- Data Structures Using C++ (Second Edition) by D.S. Malik – 2012 by D.S. Malik.

- Data Structures and Algorithms in C++ 4th Edition by Mark A. Weiss 2014.

#### 10. المرفقات: