# **Lecture 4 Logic Gates**

The term gate was introduced to describe a circuit that performs a basic logic operation.

**Logic gates** are one of the fundamental building blocks of digital systems. Most of the functions in a computer, with the exception of certain types of memory, are implemented with logic gates used on a very large scale. For example, a microprocessor, which is the main part of a computer, is made up of hundreds of thousands or even millions of logic gates.

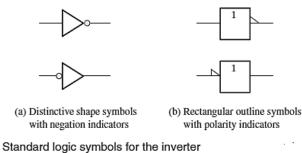

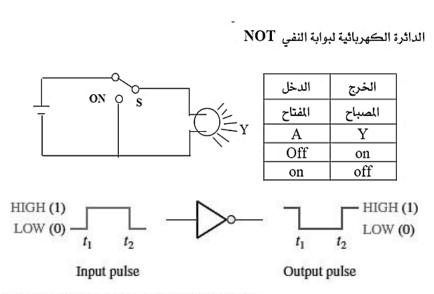

#### **NOT Gate**

Inverter operation with a pulse input.

جدول الحقيقة لبوابة NOT

| الدخل | الخرج |

|-------|-------|

| A     | Y     |

| 0     | 1     |

| 1     | 0     |

معادلة الجبر البولي لبوابة NOT

$$Y = \overline{A}$$

$$A \longrightarrow \overline{A} \longrightarrow \overline{\overline{A}} \text{ or } A$$

$A = 1 \longrightarrow \overline{\overline{A}} = 0 \qquad \therefore \quad \overline{\overline{\overline{A}}} = 1$

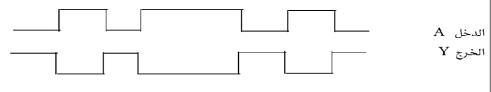

المخطط البياني الزمني لبوابة NOT

مثال: ارسم الرسم البياني الزمني لخرج بوابة النفي NOT إذا كانت إشارة الدخل كما هو موضح في الشكل التالى:

الحل:

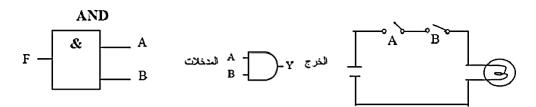

### **AND Gate**

شكل (٢ - ١) الدائرة الكهربائية لبوابة AND شكل (٢ - ٢) الرمز المنطقي لبوابة و " و " AND

| الدخل |      | الخرج |

|-------|------|-------|

| В     | Α    | Y     |

| 0     | 0    | 0     |

| 0     | 1    | 0     |

| 1     | 0    | 0     |

| 1 1   |      | 1     |

| (٢),  | جدوز |       |

| خل   | الد  | الخرج   |

|------|------|---------|

| نثاح | äll  | المصباح |

| В    | Α    | Y       |

| off  | off  | Off     |

| off  | on   | Off     |

| on   | off  | Off     |

| on   | on   | On      |

|      | (1), | جده     |

## **AND Gate Truth Table**

The logical operation of a gate can be expressed with a truth table that lists all input combinations with the corresponding outputs, as illustrated in Table for a 2-input AND

gate. The truth table can be expanded to any number of inputs. Although the terms HIGH and LOW tend to give a —physical sense to the input and output states, the truth table is shown with 1s and 0s; a HIGH is equivalent to a 1 and a LOW is equivalent to a 0 in positive logic. For any AND gate, regardless of the number of inputs, the output is HIGH only when all inputs are HIGH. The total number of possible combinations of binary inputs to a gate is determined by the following formula:

$$N = 2^n$$

where N is the number of possible input combinations and n is the number of input variables.

To illustrate, For two input variables: N = 22 = 4 combinations

For three input variables: N = 23 = 8 combinations For four input variables: N = 24 = 16 combinations

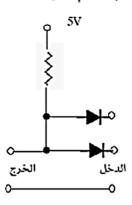

الدائرة ال إلكترونية لبوابة AND باستخدام الثنائيات

الشكل (٢) يبين تمثيل بوابة و" AND ذات مدخلين باستخدام الثناثيات وفي هذه الداثرة نجد أن:

- إذا كان الدخلان A&B "0" هإن الشائبات ستكون في حالة انحياز أمامي وبالنالي جهد الخرج صفراً.

- إذا كان أحد الدخلين A, B '0 فإن الخرج يساوي صفراً لأن أحد الثناثيات يكون في حالة الحياز أمامي.

- إذا كان الدخلان A , B "أ فإن الثنائبات ستكون في حالة انعباز عكسي وبالثالي يون جهد

الخرج مساوياً 5v أي منطقياً "1"

المعادلة البولية لبراية AND " معادلة الجبر البولي لبواية AND"

الجبر البولي Boolean Algebra هـ و أحد أشكال المنطق الرمـزي والـذي يبين كيفية عمل البوابات المنطقية والتعبير البولي هـ وسيلة اختزال لتوضيح ما يحدث في الدائرة المنطقية .

معادلة لبوابة AND ذات مدخلين

$A \cdot B = y$

Y=A and B و X=A تساوي الخرج X=A أو

| المدخلات | A<br>B<br>C | الخرج |

|----------|-------------|-------|

|----------|-------------|-------|

(أ) الرمز المنطقي لبوابة "و" AND ذات ثلاثة مداخل

(ب) معادلة الجبر البولي ذات ثلاثة مداخل

$A \cdot B \cdot C = Y$

|   | الدخل |   | الخرج |

|---|-------|---|-------|

| С | В     | A | Y     |

| 0 | 0     | 0 | 0     |

| 0 | 0     | 1 | 0     |

| 0 | 1     | 0 | 0     |

| 0 | 1     | 1 | 0     |

| 1 | 0     | 0 | 0     |

| 1 | 0     | 1 | 0     |

| 1 | 1     | 0 | 0     |

| 1 | 1     | 1 | 1     |

(ج) جدول الحقيقة لبوابة AND ذات ثلاثة مداخل

. . . . .

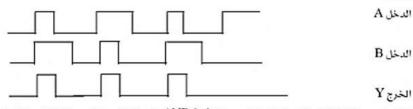

### المخطط البياني الزمني لبوابة AND " الشكل الموجي لخرج البوابة "

مثال: إرسم المغطط البيانات الزمني تخرج بوابة "و " AND ذات المدخلين إذا كانت إشارات الدخل كما هو موضح في الشكل التالي:

الحل:

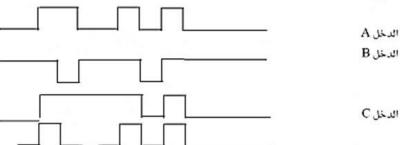

مثال: إرسم المغطط البيانات الزمني لخرج بوابة "و" AND ذات ثلاثة مداخل ، إذا كانت إشارات الدخلكما هو مبين في الشكل الثالي:

الخرج Y

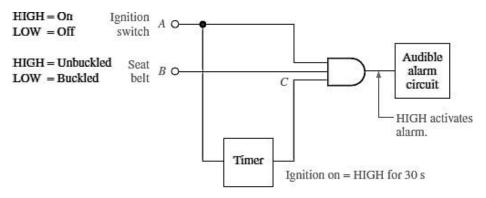

an AND gate is used in a simple automobile seat belt alarm system to detect when the ignition switch is on and the seat belt is unbuckled. If the ignition switch is on, a HIGH is produced on input A of the AND gate. If the seat belt is not properly buckled, a HIGH is produced on input B of the AND gate. Also, when the ignition switch is turned on, a timer is started that produces a HIGH on input C for 30 s. If all three conditions exist—that is, if the ignition is on and the seat belt is unbuckled and the timer is running—the output of the AND gate is HIGH, and an audible alarm is energized to remind the driver.

A simple seat belt alarm circuit using an AND gate.

يمكن استخدام بوابة آند AND في نظام انذار حزام الأمان Seat belt في السيارة، من أجل اكتشاف هل حزام الأمان مقفل Buckled أم غير مقفل Unbuckled، الشكل يظهر ذلك، نلاحظ من الشكل عناصر هذا النظام، عندما يكون مفتاح التشغيل للسيارة ignition switch=on، ينتج حالة جهد مرتفعة HIGH على المدخل A للبوابة آند AND، أيضاً وبنفس الوقت سوف يفعل المؤقت الذي يبدأ انتاج حالة مرتفعة HIGH على المدخل C للبوابة آند AND لمدة 30 ثانية، وعندما حزام الأمان غير مقفل سينتج ينتج حالة مرتفعة HIGH على المدخل B للبوابة آند AND، وبالتالي إذا كانت الشروط الثلاثة موجودة، السيارة في حالة عمل (مفتاح التشغيل في حالة مرتفعة On)، وحزام الأمان غير مقفل، والمؤقت الزمني يعمل، فإن مداخل البوابة آند AND الثلاثة في حالة مرتفعة HIGH، بالتالي خرج البوابة سيكون فيي حالة مرتفعة HIGH، ليفعل نظام التنبيه الصوق AND الذك يعلم السائق أن حزام الأمان غير مقفل.

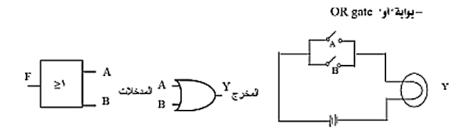

**OR GATE**

· الرمز المنطقي لبوابة "أو " OR

· الدائرة الكهربائية لبرابة OR

| الدخل | I | الخرج |

|-------|---|-------|

| В     | A | Y     |

| 0     | 0 | 0     |

| 0     | 1 | 1     |

| 1     | 0 | 1     |

| 1     | 1 | 1     |

| خل      | الد | الخرج   |

|---------|-----|---------|

| المفتاح |     | المصباح |

| В       | A   | Y       |

| off     | off | Off     |

| off     | on  | On      |

| on      | off | On      |

| on      | on  | On      |

|    | الدخل |   | الخرج |

|----|-------|---|-------|

| C  | В     | A | Y     |

| 0  | 0     | 0 | 0     |

| 0  | 0     | 1 | 1     |

| 0  | 1     | 0 | 1     |

| 0  | 1     | l | 1     |

| -1 | 0     | 0 | 1     |

| 1  | 0     | ı | 1     |

| 1  | 1     | 0 | 1     |

| 1  | 1     | 1 | 1     |

جدول الحقيقة لبوابة OR ذات الثلاثة مداخل

المخطط البيائي الزمني لبوابة OR

مثال: ارسم المغمَّك البياني الزمني لبوابة OR ذات مدخلين إذا كانت إشارات الدخل كما هو موضح في الشكل التالي ، واكتب معادلة الجبر البولي الخاصة بها ؟

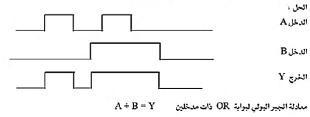

Application: A simplified portion of an intrusion detection and alarm system is shown in Figure. This system could be used for one room in a home—a room with

two windows and a door. The sensors are magnetic switches that produce a HIGH output when open and a LOW output when closed. As long as the windows and the door are secured, the switches are closed and all three of the OR gate inputs are LOW. When one of the windows or the door is opened, a HIGH is produced on that input to the OR gate and the gate output goes HIGH. It then activates and latches an alarm circuit to warn of the intrusion.

يمكن استخدام بوابة أور OR في نظام للتنبيه وكشف التطفل أو السرقة الموضح في الشكل )، هذا النظام يمكن أن يستخدم في غرفة لها نافذتان وباب واحد، المستشعرات تكون مفاتيح مغناطيسية تنتج الخرج المرتفع HIGH عند الفتح، والخرج المنخفض LOW عند الاغلاق، هذه المفاتيح توصل إلى مداخل بوابة أور OR، طالما النوافذ والباب مغلقة ومؤمنة، المفاتيح مغلقة وجميع مداخل البوابة أور OR تكون بجهد مرتفع LOW، عندما أحد النوافذ، أو الباب يفتح، ينتج جهد مرتفع HIGH على

أحد مداخل البوابة أور OR، وبالتالي خرج البوابة يصبح بجهد مرتفع HIGH، والذي يفعل دائرة تنبيه للتحذير من وجود متطفل أو وجود أحد قام بالفتح.

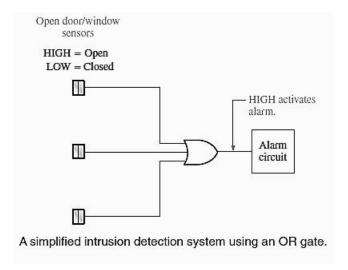

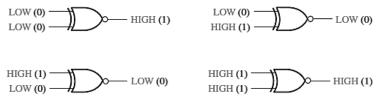

### **The NAND Gate**

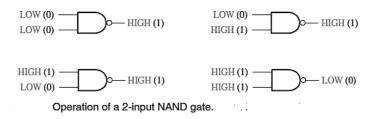

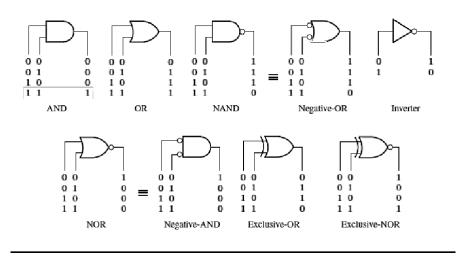

The term NAND is a contraction of NOT-AND and implies an AND function with a complemented (inverted) output. The standard logic symbol for a 2-input NAND gate and its equivalency to an AND gate followed by an inverter are shown in Figure where the symbol K means equivalent to. A rectangular outline symbol is shown in part (b).

### **Operation of a NAND Gate**

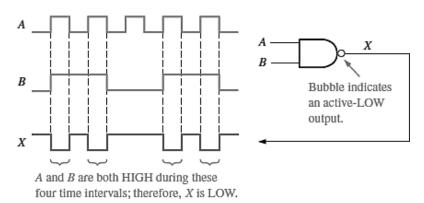

**Example:** If the two waveforms A and B shown in Figure are applied to the NAND gate inputs, determine the resulting output waveform.

# Negative-OR Equivalent Operation of a NAND Gate

For a 2-input NAND gate performing a negative-OR operation, output X is HIGH when either input A or input B is LOW, or when both A and B are LOW.

standard symbols representing the two equivalent operations of a NAND gate.

#### **Example:**

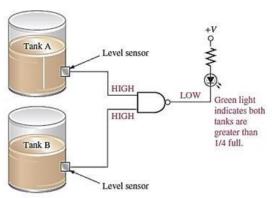

Two tanks store certain liquid chemicals that are required in a manufacturing process. Each tank has a sensor that detects when the chemical level drops to 25% of full. The sensors produce a HIGH level of 5 V when the tanks are more than one-quarter full. When the volume of chemical in a tank drops to one-quarter full, the sensor puts out a LOW level of 0 V. It is required that a single green light-emitting diode (LED) on an indicator panel show when both tanks are more than one-quarter full. Show how a NAND gate can be used to implement this function.

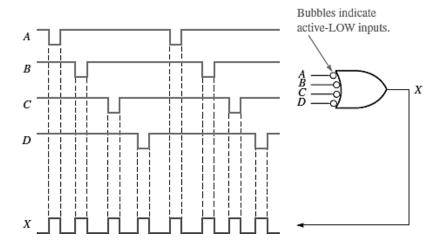

As long as both sensor outputs are HIGH (5 V), indicating that both tanks are more than one-quarter full, the NAND gate output is LOW (0 V). The green LED circuit is connected so that a LOW voltage turns it on. The resistor limits the LED current. **Example**: for the 4-input NAND gate in, operating as a negative-OR gate, determine the output with respect to the inputs.

The output waveform X is HIGH any time an input waveform is LOW as shown in the timing diagram.

### **The NOR Gate**

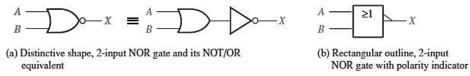

The term NOR is a contraction of NOT-OR and implies an OR function with an inverted (complemented) output. The standard logic symbol for a 2-input NOR gate and its equivalent OR gate followed by an inverter are shown in Figure (a). A rectangular outline symbol is shown in part (b).

Standard NOR gate logic symbols

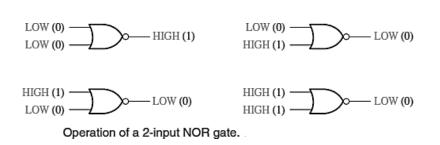

#### **Operation of a NOR Gate**

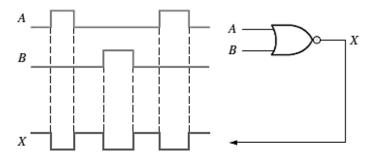

**Example**: If the two waveforms shown in Figure 3–36 are applied to a NOR gate, what is the resulting output waveform?

Truth table for a 2-input NOR gate.

| Inp              | uts              | Output |

|------------------|------------------|--------|

| $\boldsymbol{A}$ | $\boldsymbol{B}$ | X      |

| 0                | 0                | 1      |

| 0                | 1                | 0      |

| 1                | 0                | 0      |

| 1                | 1                | 0      |

|                  | CII A I          | OW     |

1 = HIGH, 0 = LOW.

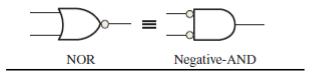

## **Negative-AND Equivalent Operation of the NOR Gate**

For a 2-input NOR gate performing a negative-AND operation, output X is HIGH only when both inputs A and B are LOW.

Standard symbols representing the two equivalent operations of a NOR gate.

**Example:** A device is needed to indicate when two LOW levels occur simultaneously on its inputs and to produce a HIGH output as an indication. Specify the device.??

**Solution**: A 2-input NOR gate operating as a negative-AND gate is required to produce a HIGH output when both inputs are LOW, as shown in Figure

# **The Exclusive-OR and Exclusive-NOR Gates**

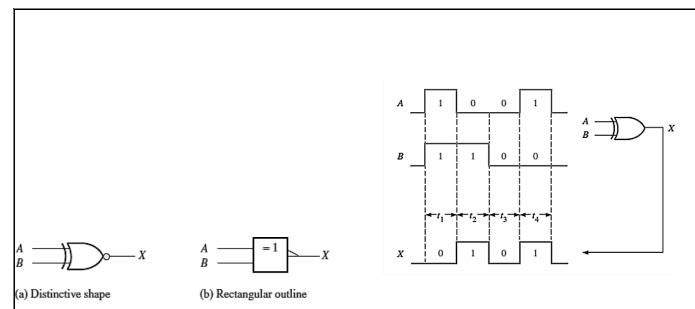

Standard symbols for an exclusive-OR (XOR for short) gate are shown in Figure The XOR gate has only two inputs.

For an exclusive-OR gate, output X is HIGH when input A is LOW and input B is HIGH, or when input A is HIGH and input B is LOW; X is LOW when A and B are both HIGH or both LOW.

A

$$\longrightarrow$$

A  $\bigoplus$  B  $\longrightarrow$  B  $\longrightarrow$  A  $\bigoplus$  B  $\longrightarrow$  C (a) Distinctive shape (b) Rectangular outline

Standard logic symbols for the exclusive-OR gate.

## The Expression Logic for EX-OR Gate:

$$A \oplus B$$

. . . is equivalent to . .

| Inputs           |                  | Output |

|------------------|------------------|--------|

| $\boldsymbol{A}$ | $\boldsymbol{B}$ | X      |

| 0                | 0                | 0      |

| 0                | 1                | 1      |

| 1                | 0                | 1      |

| 1                | 1                | 0      |

$$A \oplus B = A\overline{B} + \overline{A}B$$

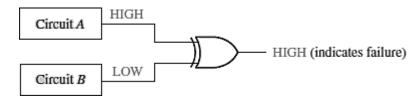

**Application:** A certain system contains two identical circuits operating in parallel. As long as both are operating properly, the outputs of both circuits are always the same. If one of the circuits fails, the outputs will be at opposite levels at some time. Devise a way to monitor and detect that a failure has occurred in one of the circuits.

يمكن استخدام البوابة اكس أور XOR Gate، في نظام لكشف العطل في دائرتين يعملان على التفرع، يوصل خرجهما على مدخل بوابة اكس أور XOR، كما هو موضح في الشكل ، طالما هاتان الدائرتان تعملان بشكل صحيح، فإن خرج الدئراتين متشابه وخرج البوابة اكس أور XOR في حالة جهد منخفض LOW، وإذا حدث عطل في إحدى الدائرتين فإن خرج الدائرتين سيكون مخلتف، وبالتالي خرج البوابة سيكون في حالة جهد مرتفع HIGH إشارة إلى وجود عطل في أحد الدوائر.

**Example** of exclusive-OR gate operation with pulse waveform inputs.

Standard logic symbols for the exclusive-NOR gate.

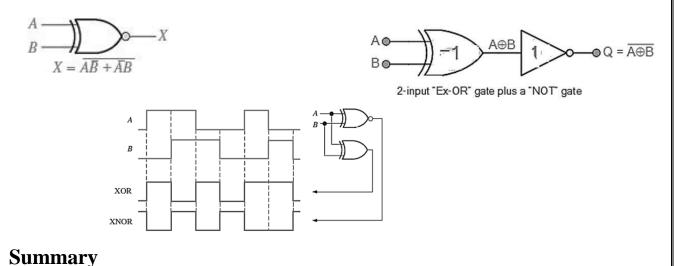

## **The Exclusive-NOR Gate**

For an exclusive-NOR gate, output X is LOW when input A is LOW and input B is HIGH, or when A is HIGH and B is LOW; X is HIGH when A and B are both HIGH or both LOW.

The four possible input combinations and the resulting outputs for an XNOR gate are shown in Figure The operation of an XNOR gate is summarized in Table. Notice that the output is HIGH when the same level is on both inputs.

Example: Determine the output waveforms for the XOR gate and for the XNOR gate,

given the input waveforms, A and B, in the Figure

- 2. A NOT gate cannot have more than one input.

- 3. If any input to an OR gate is zero, the output is zero.

- 4. If all inputs to an AND gate are 1, the output is 0.

- 5. A NAND gate can be considered as an AND gate followed by a NOT gate.

- 6. A NOR gate can be considered as an OR gate followed by an inverter

All possible logic levels for an exclusive-NOR gate.

Truth table for an exclusive-NOR gate.

|                  | Inputs | Output |

|------------------|--------|--------|

| $\boldsymbol{A}$ | В      | X      |

| 0                | 0      | 1      |

| 0                | 1      | 0      |

| 1                | 0      | 0      |

| 1                | 1      | 1      |